Version 1.20

June 15, 2022

NATIONAL INSTITUTE OF ADVANCED INDUSTRIAL SCIENCE AND TECHNOLOGY (AIST)

|    |         |           | Contents                                      |    |

|----|---------|-----------|-----------------------------------------------|----|

| Re | evision | history   |                                               | 5  |

| 0  | Prefac  | ee        |                                               | 6  |

|    | 0.1     | Object    | of document                                   | 6  |

|    | 0.2     | Referen   | nces                                          | 6  |

|    | 0.3     | Termin    | nology                                        | 7  |

|    | 0.4     | Abbrev    | viation                                       | 8  |

| 1  | PP int  | roductio  | on                                            | 10 |

|    | 1.1     | PP refe   | erence identification                         | 10 |

|    | 1.2     | TOE ov    | verview                                       | 10 |

|    |         | 1.2.1     | Composition of the TOE                        | 10 |

|    |         | 1.2.2     | Security features of the TOE                  | 12 |

|    |         | 1.2.3     | Use case of the TOE                           | 13 |

|    |         | 1.2.4     | Roles                                         | 13 |

|    |         | 1.2.5     | Life cycle of the TOE                         | 14 |

|    |         | 1.2.6     | Protection of keys                            | 16 |

| 2  | Confo   | rmance    | claims                                        | 17 |

| 3  | Secur   | ity probl | em definition                                 | 18 |

|    | 3.1     | Assets    |                                               | 18 |

|    | 3.2     | Threats   | S                                             | 18 |

|    | 3.3     | Organia   | zational security policy                      | 20 |

|    | 3.4     | Assum     | ptions                                        | 20 |

| 4  | Secur   | ity objec | etives                                        | 21 |

| _  | 4.1     |           | ry objectives for the operational environment | 21 |

| 5  |         | ity requi |                                               | 22 |

|    | 5.1     |           | ry functional requirements                    | 22 |

|    |         | 5.1.1     | Cryptographic support                         | 22 |

|    |         | 5.1.2     | User data protection                          | 23 |

|    |         | 5.1.3     | Protection of the TSF                         | 25 |

|    | 5.2     |           | y assurance requirements                      | 28 |

|    | 5.3     | Securit   | ry requirements rationale                     | 28 |

|    |         | 5.3.1     | Security functional requirements rationale    | 28 |

|    |         | 5.3.2     | Security assurance requirements rationale     | 29 |

| 6  | Annei   | idix: Ext | tended component definitions                  | 32 |

| <u>P</u> 1 | rotecti     | on Prot    | ile for Single Chip Microcontroller equipped with a secure cryptograph | ic unit  |

|------------|-------------|------------|------------------------------------------------------------------------|----------|

|            | 6.1         | Extende    | ed security functional components                                      | 32       |

|            |             | 6.1.1      | FCS_KDF_EXT Cryptographic key derivation                               | 32       |

|            |             | 6.1.2      | FCS_RBG_EXT Random bit generation                                      | 32       |

|            |             | 6.1.3      | FCS_SNI_EXT Salt, Nonce, and Initialisation Vector Generation          | 33       |

|            |             | 6.1.4      | FCS_STG_EXT.1 Secure Key Storage                                       | 34       |

|            |             | 6.1.5      | FDP_MFW_EXT.1 Integrity and authenticity of the software               | 36       |

|            |             | 6.1.6      | FPT_EMS_EXT Mitigation of leak from the TOE                            | 36       |

|            |             | 6.1.7      | FPT_TUD_EXT.1 Trusted update                                           | 37       |

|            | 6.2         | Extende    | ed security assurance component                                        | 38       |

|            |             | 6.2.1      | AVA_SCU_EXT Vulnerability assessment of the SCU                        | 38       |

|            |             | 6.2.2      | Vulnerability survey of the SCU (Extended – AVA_SCU_EXT)               | 38       |

| 7          | Apper       | ndix: Sele | ection-based security functional requirements                          | 40       |

|            | 7.1         |            | graphic support                                                        | 40       |

| 8          |             |            | tion-based security functional requirements                            | 45       |

| 9          | 8.1         | ,,,        | graphic support  A SCU EXT - Vulnerability survey of the SCU           | 45<br>48 |

|            | 9.1         |            | cation of factors and rating attack potential                          | 48       |

|            | <i>J</i> .1 | 9.1.1      | How to compute an attack                                               | 48       |

|            |             | 9.1.2      | Elapsed time                                                           | 48       |

|            |             | 9.1.3      | Expertise                                                              | 49       |

|            |             | 9.1.4      | Knowledge of TOE                                                       | 49       |

|            |             | 9.1.5      | Access to TOE                                                          | 49       |

|            |             | 9.1.6      | Equipment                                                              | 50       |

|            |             | 9.1.7      | Open Samples/Samples with known Secrets                                | 50       |

|            |             | 9.1.8      | Calculation of attack potential                                        | 51       |

|            |             | 9.1.9      | Attacker Profiles in the TOE                                           | 52       |

|            |             | 9.1.10     | Ratings of attack potential in this TOE                                | 54       |

|            | 9.2         |            | es of attack                                                           | 56       |

|            |             | 9.2.1      | Physical attack                                                        | 56       |

|            |             | 9.2.2      | Overcoming sensors and filters                                         | 57       |

|            |             | 9.2.3      | Perturbation attacks, Attack on RNG, Exploitation of test features     | 57       |

|            |             | 9.2.4      | Side-channel attacks                                                   | 58       |

|            |             | 9.2.5      | Software attacks                                                       | 58       |

|            |             |            |                                                                        |          |

| Protection Profile for Single Chip Microcontroller equipped with a secure cryptographic unit |

|----------------------------------------------------------------------------------------------|

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

## **Revision history**

| Version | Date          | Description                                              |

|---------|---------------|----------------------------------------------------------|

| 1.20    | June 15, 2022 | Revised in accordance with comments from evaluation body |

## Acknowledgements

This Protection Profile (PP) was developed by the SCU Inside System Committee with representatives from universities, national institutes, security service providers, industries, and the Information Technology Security Evaluation Facility. The organizations that directly contributed to the development of this PP include:

National Institute of Advanced Industrial Science and Technology (AIST)

Yokohama National University (YNU)

SECOM Co., Ltd.

Toppan Technical Design Center Co., Ltd.

STMicroelectronics

Electronic Commerce Security Technology Research Association (ECSEC TRA)

ECSEC Laboratory Inc.

## 0 Preface

## 0.1 Object of document

This document presents the Protection Profile (PP) to express the Security Functional Requirements (SFRs) and Security Assurance Requirements (SARs) for a Protection Profile for Single Chip Microcontroller equipped with a secure cryptographic unit (SCU).

## 0.2 References

| [180-4]   | FIPS PUB 180-4 FEDERAL INFORMATION PROCESSING STANDARDS PUBLICATION Secure Hash Standard (SHS)                                               |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| [186-4]   | FIPS PUB 186-4 FEDERAL INFORMATION PROCESSING STANDARDS PUBLICATION Digital Signature Standard (DSS)                                         |

| [202]     | FIPS PUB 202 FEDERAL INFORMATION PROCESSING STANDARDS PUBLICATION SHA-3 Standard: Permutation-Based Hash and Extendable-Output Functions     |

| [800-38A] | NIST Special Publication 800-38A Recommendation for Block Cipher Modes of Operation Methods and Techniques                                   |

| [800-38B] | NIST Special Publication 800-38B Recommendation for Block Cipher Modes of Operation: the CMAC Mode for Authentication                        |

| [800-38C] | NIST Special Publication 800-38C Recommendation for Block Cipher Modes of Operation: The CCM Mode for Authentication and Confidentiality     |

| [800-38D] | NIST Special Publication 800-38D Recommendation for Block Cipher Modes of Operation: Galois/Counter Mode (GCM) and GMAC                      |

| [800-38E] | NIST Special Publication 800-38E Recommendation for Block Cipher Modes of Operation: The XTS-AES Mode for Confidentiality on Storage Devices |

| [800-38F] | NIST Special Publication 800-38F Recommendation for Block Cipher Modes of Operation: Methods for Key Wrapping                                |

| [800-90B] | NIST Special Publication 800-90B Recommendation for the Entropy Sources Used for Random Bit Generation                                       |

| [800-108] | NIST Special Publication 800-108 Recommendation for Key Derivation Using Pseudorandom Functions (Revised)                                    |

| [800-133] | NIST Special Publication 800-133 Revision 1 Recommendation for Cryptographic Key Generation                                                  |

| [1619]    | IEEE 1619-2018 - IEEE Standard for Cryptographic Protection of Data on Block-Oriented Storage Devices                                        |

| [5639]    | RFC 5639 Elliptic Curve Cryptography (ECC) Brainpool Standard Curves and Curve Generation                                                    |

| [8032]    | RFC 8032 Edwards-Curve Digital Signature Algorithm (EdDSA)                                                                                   |

| [8439]    | RFC 8439 ChaCha20 and Poly1305 for IETF Protocols                                                                                            |

| Protection Profile for Single ( | Chip Microcontroller equippe | ed with a secure cryptographic unit |

|---------------------------------|------------------------------|-------------------------------------|

|                                 |                              |                                     |

| 110100111111 | and for single only interestinated equipped with a secure orygen-graphic since                                                                              |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [9797-2]     | ISO/IEC 9797-2:2011 Information technology - Security techniques - Message Authentication Codes (MACs) - Part 2: Mechanisms using a dedicated hash-function |

| [10116]      | ISO/IEC 10116:2017 Information technology - Security techniques - Modes of operation for an n-bit block cipher                                              |

| [10118-3]    | ISO/IEC 10118-3:2018 IT Security techniques - Hash-functions - Part 3: Dedicated hash-functions                                                             |

| [14888-3]    | ISO/IEC 14888-3:2018 IT Security techniques - Digital signatures with appendix - Part 3: Discrete logarithm based mechanisms                                |

| [18031]      | ISO/IEC 18031:2011 Information technology - Security techniques - Random bit generation                                                                     |

| [18033-3]    | ISO/IEC 18033-3:2010 Information technology - Security techniques - Encryption algorithms - Part 3: Block ciphers                                           |

| [19772]      | ISO/IEC 19772:2009 Information technology - Security techniques - Authenticated encryption                                                                  |

| [AAPS]       | Joint Interpretation Library, Application of Attack Potential for Smartcards and Similar Devices, Version 3.1, June 2020                                    |

| [AMSS]       | Joint Interpretation Library, Application of Attack Potential for Smartcards and Similar Devices, Version 2.4, January 2020                                 |

| [CC1]        | Common Criteria for Information Technology Security Evaluation, Part 1: Introduction and General Model, Version 3.1 Revision 5, April 2017.                 |

| [CC2]        | Common Criteria for Information Technology Security Evaluation, Part 2: Security Functional Components, Version 3.1 Revision 5, April 2017.                 |

| [CC3]        | Common Criteria for Information Technology Security Evaluation, Part 3: Security Assurance Components, Version 3.1 Revision 5, April 2017.                  |

| [CEM]        | Common Methodology for Information Technology Security Evaluation, Evaluation Methodology, Version 3.1, Revision 5, April 2017.                             |

| [CPPFDE]     | collaborative Protection Profile for Full Drive 1 Encryption - Encryption Engine Version 2.0 September 09, 2016                                             |

| [PP0096]     | Common Criteria Protection Profile FIDO Universal Second Factor (U2F) Authenticator BSI-PP-CC-0096-V3-2018                                                  |

| [PPTEE]      | GlobalPlatform Device Committee TEE Protection Profile Version 1.2.1                                                                                        |

## 0.3 Terminology

| Terminology          | Description                                                                                                                               |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Application software | From the viewpoint of the TOE, application software is user data that uses the encryption service of the SCU via a software gate API.     |

| External entity      | Human or IT entity potentially interacting with the TOE from outside its boundary.                                                        |

| Garbage collection   | Reclaiming memory occupied by objects that are no longer in use by the program.                                                           |

| Hardware gate        | A hardware gate is a hardware component of an access control mechanism for a cryptographic function that accesses a cryptographic engine. |

| Terminology             | Description                                                                                                                                                                                    |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware gate key (HGK) | A key as a Root of Trust (RoT).                                                                                                                                                                |

| Intermediate key        | A Key Encryption Key (KEK) or Key Wrapping Key (KWK) used to protect a Data Encryption Key (DEK) and MAC key.                                                                                  |

| Protected storage       | Specialised storage for the HGK. It may be an OTP area where the HGK is written by a semiconductor test process or hard coded to be a part of a circuit.                                       |

| Secrets                 | In this PP, it refers to data that requires confidentiality protection, such as pre-<br>shared keys, key material, and pre-calculated values.                                                  |

| Submask                 | A bit string that can be generated and stored in a number of ways.                                                                                                                             |

| Software gate           | A software gate is a software component of an access control mechanism for a cryptographic function that provides cryptographic function to the application software via a hardware component. |

| User Keys               | Keys used by the application software that are encrypted by the KEK. Data for integrity checks are attached.                                                                                   |

## 0.4 Abbreviation

| Abbreviation | Description                                                                                                                                                   |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AES          | Advanced Encryption Standard                                                                                                                                  |  |

| API          | Application Program Interface, an interface between different parts of a computer program intended to simplify the implementation and maintenance of software |  |

| CBC          | Cipher Block Chaining                                                                                                                                         |  |

| CC           | Common Criteria                                                                                                                                               |  |

| CCM          | Counter with CBC-MAC                                                                                                                                          |  |

| CMAC         | Cipher-based Message Authentication Code                                                                                                                      |  |

| CPU          | Central Processing Unit                                                                                                                                       |  |

| CTR          | Counter                                                                                                                                                       |  |

| DEK          | Data Encryption Key                                                                                                                                           |  |

| DRBG         | Deterministic Random Bit Generator                                                                                                                            |  |

| ECC          | Elliptic Curve Cryptography                                                                                                                                   |  |

| ECDSA        | Elliptic Curve Digital Signature Algorithm                                                                                                                    |  |

| EdDSA        | Edwards-curve Digital Signature Algorithm                                                                                                                     |  |

| GCM          | Galois/Counter Mode                                                                                                                                           |  |

| FIPS         | Federal Information Processing Standard(s)                                                                                                                    |  |

| HGK          | Hardware Gate Key                                                                                                                                             |  |

| HMAC         | Keyed-Hash Message Authentication Code                                                                                                                        |  |

| IEEE         | Institute of Electrical and Electronics Engineers                                                                                                             |  |

| IEC          | International Electrotechnical Commission                                                                                                                     |  |

| Abbreviation | Description                                                                     |  |

|--------------|---------------------------------------------------------------------------------|--|

| IoT          | Internet of Things                                                              |  |

| IP           | Intellectual Property, a semiconductor intellectual property                    |  |

| ISO          | International Organization for Standardization                                  |  |

| IT           | Information Technology                                                          |  |

| IV           | Initialisation Vector                                                           |  |

| KDF          | Key Derivation Functions                                                        |  |

| KEK          | Key Encryption Key                                                              |  |

| KW           | Key Wrap                                                                        |  |

| KWK          | Key Wrapping Key                                                                |  |

| KWP          | Key Wrap With Padding                                                           |  |

| MAC          | Message Authentication Code                                                     |  |

| NIST         | National Institute of Standards and Technology                                  |  |

| OTP          | One Time Programmable                                                           |  |

| PP           | Protection Profile                                                              |  |

| RBG          | Random Bit Generator                                                            |  |

| RoT          | Root of Trust                                                                   |  |

| SAR          | Security Assurance Requirement                                                  |  |

| SCU          | Secure Cryptographic Unit                                                       |  |

| SFP          | Security Functional Policy                                                      |  |

| SFR          | Security Functional Requirement                                                 |  |

| SHA          | Secure Hash Algorithm                                                           |  |

| SoC          | System on a Chip                                                                |  |

| ST           | Security Target                                                                 |  |

| TOE          | Target of Evaluation                                                            |  |

| TSF          | TOE Security Function                                                           |  |

| XTS          | XEX (XOR – Encrypt – XOR) based tweaked-codebook mode with cipher text stealing |  |

## 1 PP introduction

### 1.1 PP reference identification

PP Reference Protection Profile for Single Chip Microcontroller equipped with a secure cryptographic unit

Version 1.20

Date June 15, 2022

#### 1.2 TOE overview

### 1.2.1 Composition of the TOE

The Target of Evaluation (TOE) is a Single Chip Microcontroller equipped with a secure cryptographic unit (SCU). The SCU consists of a cryptographic engine, and software and hardware gates that can access the cryptographic engine via "software gate APIs." The assumed TOE is a built-in memory type in a single-chip microcontroller. An external memory type that has large-scale memory outside the single-chip microcontroller is assumed as another type of TOE; however, this is a future challenge.

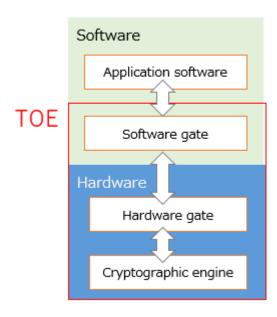

Figure 1-1 Conceptual diagram of the SCU

The TOE is generally distributed in the form of a SoC. In the case of the TOE with built-in memory, it is packaged by mounting it on a single die. This SoC is soldered on a board on which various circuits necessary for embedded device applications are mounted, and the board is placed in the housing of the embedded device.

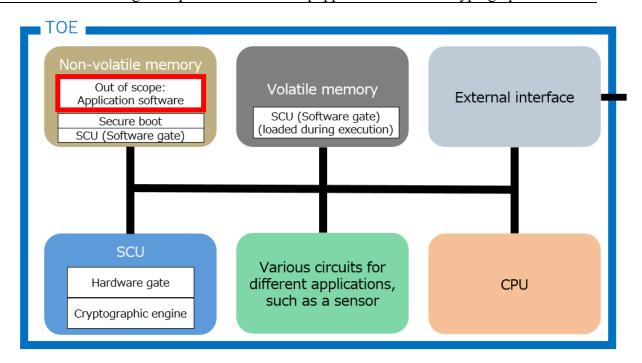

Figure 1-2 shows an example of the TOE configuration. The blue line shows the physical boundary of the TOE and the configuration of a typical microcontroller equipped with an SCU. The red line shows the logical boundary of the TOE. In Figure 1-2, the application software is logically located outside the TOE and uses cryptographic functions through the software and hardware gates. The application software is stored in non-volatile memory inside the physical boundary of the TOE.

Figure 1-2 TOE configuration example

The software and hardware gates are mechanisms for controlling access to the cryptographic functions, and they correspond to software and hardware components of the access control function. Access to the cryptographic functions by the application software is legitimate and should be permitted, but access by others must be denied. The TOE access control mechanism is implemented to distinguish between these accesses.

The software and hardware gates operate as follows. Each time the hardware gate receives cryptographic command data directed at it, it transitions its internal state. This is uniquely determined by the previous internal state and the current input (cryptographic command data). If the hardware gate knows the correct transition data of the internal state, it can compare the result of the transition by the current input with the correct transition data to determine whether the input command data is legitimate.

The software gates provide information to manage the state transitions of the hardware gates. All patterns of access to the cryptographic functions, which are unique and predicted in advance by the developer, are known only to the developer. The internal state transitions of the hardware gate associated with these access patterns are calculated in advance and stored in the software gate. When the software gate receives the access command data to the cryptographic function from the application software, it transfers both the access command data and the next internal state transition data of the hardware gate to the hardware gate. The hardware gate checks the internal state transition data passed to it against the internal state transition results from the command data received at the same time, and if the two match, it determines that the received command data is legitimate. Software gates, which contain internal state transition data to be passed to hardware gates, are stored in non-volatile memory in the TOE at the time of TOE manufacturing and cannot be generated except by developers. In other words, the access pattern to the cryptographic function calculated in advance by the developer will be executed, but if an emulator or other device tries to use the cryptographic function with any other pattern, it will not be able to provide the encrypted internal state transition data and the hardware gate will deny access.

The components labeled as software and hardware gates in Figure 1-2 depend on the implementation of the SCU; to protect the integrity of the contents of the memory located outside the SCU and the integrity of the cipher processing, the application software should be developed to use software gates appropriately.

The SCU has a self-protection function to protect its own security function. The TOE stores the HGK, which is the RoT, and information that uniquely identifies the TOE to external entities in the TOE. It is the responsibility of the TOE developer to generate a random number HGK with sufficient entropy.

The TOE's secure boot program extracts the software gate and application software into RAM at startup, verifies the integrity of the software gate, and verifies the integrity (and optionally the authenticity) of the application software. The TOE also verifies the integrity and authenticity of the application software when updating it, and updates it after successful verification. Here, authenticity refers to the property that the application software was developed by a legitimate application software developer.

## 1.2.2 Security features of the TOE

The SCU provides a set of cryptographic functions as a basis for security. The TOE provides the functions to application software via software gate. The application software implements security functions such as communication protocol, memory encryption, and identification/authentication using cryptographic functions. The TOE also implements the cryptographic functions and self-protection functions that protect the security functions using the cryptographic function.

The main security functions provided by the TOE are as follows. These functions are baseline requirements, hence TOE's mandatory requirements.

- Monitoring access to the cryptographic function: The ability to detect and respond to unauthorized use of the cryptographic function by an attacker through the cooperative operation of the software and hardware gates.

- Self-protection function: The ability to prevent unauthorized use of leakage during SCU operation and the ability to detect and respond to physical attacks.

- Secure boot function: The ability to verify the integrity of the software gate and the application software during startup.

- Store keys: The ability to provide key storage whose confidentiality and integrity are protected by cryptography in order to store the keys in the memory area of the TOE outside the SCU.

- Import user keys: The ability to import key storage containing user keys and secret information from external entities to the TOE while protecting confidentiality.

- Update function: The ability to update after verifying the authenticity and integrity of the application software.

The cryptographic functions for achieving the baseline functions of the TOE are as follows. The Security Target (ST) author selects the required Security Functional Requirement (SFR) from Chapter 7.

- Encryption/Decryption: To protect confidentiality, a plaintext is encrypted into a cipher text and a cipher text is decrypted into a plaintext.

- > Digital signature verification: Verifying the digital signature for authenticity and integrity verification.

- Calculation of hash value: cryptographic hash functions calculate hash values.

- MAC generation and verification: Attaching a MAC and verifying the integrity of data with the MAC.

- Random bit generation: The TOE generates random bits and provides them for the application software.

- ➤ Using salt, nonce and generating IV: Appropriate use of salts and nonces required for cryptographic functions and generating IVs.

- Deriving keys: It derives keys.

Encrypt key: It encrypts the keys using KEKs.

The cryptographic functions provided by the TOE to the application software via the software gate are as follows. These functions are optional features, and the ST author selects the necessary SFRs from Chapter 8.

- ➤ Key generation: Keys suitable for the cryptographic algorithm and use are generated by the Random Bit Generator (RBG) of the TOE.

- Destruction of keys and key materials: Making the keys and key materials stored in the volatile memory unrecoverable. Note that the keys stored in the key storage of non-volatile memory are encrypted and are not expected to be destroyed.

- Digital signature generation: Generate a digital signature for the protection of authenticity and integrity.

#### 1.2.3 Use case of the TOE

The TOE equipped with the SCU is a microcontroller for embedded devices known as IoT edge devices such as sensors, actuators, and surveillance cameras. It is conceivable that the microcontroller, which is the TOE, has functions to process raw data collected by those devices, securely store the processed information, and securely transfer it outside the device. The SCU is a RoT for secure processing. The embedded device manufacturer defines a security policy of the embedded device, decides the information for protecting confidentiality and that for protecting integrity, and implements the application software.

The TOE protects the confidentiality, integrity, and authenticity of data handled by the application software by using its services in accordance with the instructions of the application software. That is, the TOE cannot determine which data should be protected. For example, the TOE cannot protect the confidentiality of data stored in memory in plain form or data sent to the outside in plain form. Therefore, developers who implement the application software using the TOE must identify the data they want to protect and must protect the data using the SCU.

#### **1.2.4** Roles

The main target audience for this PP is TOE developers. TOE developers purchase SCU IPs or develop them themselves, develop and manufacture single chip microcontrollers by integrating necessary components such as CPU and memory. The TOE developers also store an HGK in the SCU when the TOE is manufactured. TOE manufacturing may be manufactured at the TOE developers' factory or outsourced to a manufacturing company.

TOE users are embedded device developers who purchase the TOE and incorporate the application software into it to develop and manufacture embedded devices. Therefore, TOE guidance will be distributed to embedded device developers.

The TOE developers never manage embedded devices and do not need to inform the embedded device developer about the HGK. It is assumed that the user keys will be imported to the embedded device developer before TOE delivery. Optionally, to update the user keys, the embedded device developer can also implement a software gate API call in the application software to import the user keys.

End consumers purchase and use the embedded device equipped with the TOE. Management of the embedded device may occur via the application software outside the TOE. However, because the TOE is based on the application software implementation, management is related to the embedded device, not the TOE.

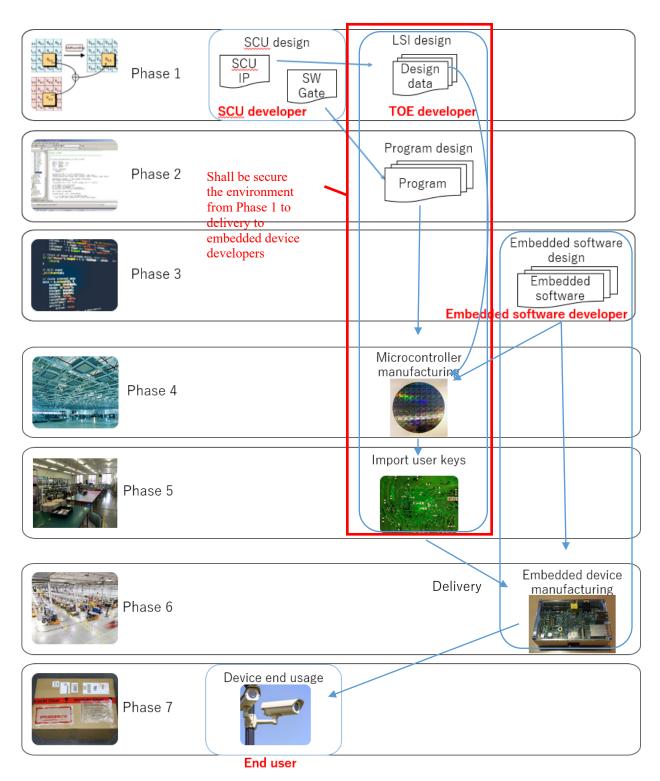

## 1.2.5 Life cycle of the TOE

The TOE developer shall secure the process from TOE development in Phase 1 to TOE manufacturing in Phase 4, and the delivery of the TOE to embedded device developers in Phase 6. The TOE developer or key installation providers must also secure the importing user key in Phase 5.

The environment for application software development in Phase 3, embedded device manufacturing in Phase 6, and distribution to end consumers in Phase 7 are outside the scope of this PP, but it is assumed that the embedded device developer who purchased the TOE will take responsibility for maintaining the development environment security.

#### Phase 1: Developing hardware

Development of the TOE. The TOE developer purchases an IP of the SCU or develops the SCU and constructs the hardware TOE together with components such as a CPU.

#### Phase 2: Purchasing software or developing program

The TOE developer purchases the software gate for secure use of the cryptographic engine from the SCU IP vendor or develops their own software gate. The TOE developer purchases a secure boot program from the SCU IP vendor or develops their own secure boot program.

#### Phase 3: Developing the application software

The embedded device developer develops the application software for embedded devices. When requesting the TOE manufacturer to install the application software, the embedded device developer sends the application software to the TOE developer. If the embedded device developer installs the application software, it will be installed in Phase 6.

#### Phase 4: Manufacturing the TOE

The TOE developer manufactures the TOE, writes the HGK, and installs the secure boot and software gate into the non-volatile memory of the TOE. If requested by the embedded device developer, the TOE developer receives the application software developed by the embedded device developer in Phase 3 and loads it into the non-volatile memory of the TOE. Note that the application software may be mounted on the TOE in Phase 6 instead of this phase. The manufactured TOE becomes a product after a developer test.

#### Phase 5: Importing the user keys

The TOE developer generates a data object (key storage) to store user keys and secret information. The TOE developer receives the user key and secret information used by the application software from the embedded device developer and stores them in key storage, and the entire key storage is encrypted and assigned a MAC. The TOE writes the key storage to the TOE's non-volatile memory via a software gate. Key importing may be performed by the TOE developer or outsourced to a key installation provider. In any case, it is necessary that key delivery and importing are performed in a secure environment. After writing the key, the TOE will be distributed from Phase 5 to Phase 6.

### Phase 6: Manufacturing the embedded device

The embedded device developer manufactures the embedded device and mounts the TOE on the embedded device. In a number of cases, the embedded device developer installs the application software into the TOE. This development process may be divided into the development of a board on which the TOE is mounted and that of the embedded device on which it is mounted. The TOE in this process is assumed to be handled securely. The completed embedded device is distributed to the end consumer.

#### Phase 7: Operating by end consumers

The final phase of the TOE life cycle. It is used under the assumed operating environment with the TOE installed in the embedded device. The threats assumed by this PP occur during this operation phase.

Figure 1-3 Life cycle of the TOE

## 1.2.6 Protection of keys

The TOE provides key storage services and keeps cryptographic keys used by the cryptographic engine confidential and secure by encrypting them. The integrity of a key is protected by a MAC. As an example, when the cryptographic key used in the hardware gate is held in non-volatile memory outside the SCU and inside the TOE, the following processing is performed. First, at the TOE developer's factory or outsourced key installation provider in Phase 5, the KEK and MAC keys are derived from the HGK written inside the SCU. Next, the key storage (which contains user keys and other data) used in the TOE is encrypted using KEK, and a MAC is assigned to the encrypted key storage using the MAC key. In this way, the key storage is stored into the memory in the TOE but out of the SCU in a state of being encrypted and attached with a MAC.

The TOE has a data object (protected storage) created by the manufacturer at the time of manufacturing, and the TOE developer stores the HGK in that data object. For example, the TOE developer generates an HGK with an RBG outside the TOE and embeds it in the TOE during the manufacturing process. The HGK guarantees the integrity of the TOE and is the starting point for permissions to other data objects (key storage). Since the HGK must be protected, the TOE needs a self-protection function.

## 2 Conformance claims

This PP is CC version 3.1 revision 5 (Japanese) conformant.

This PP conforms to CC part 2 extended and CC part 3 extended. Extended components are defined in Chapter 6.

This PP does not claim conformance to any another PP.

The TOE conformance to this PP is EAL 1 augmented with ASE\_SPD.1, ADV\_ARC.1, ADV\_FSP.2, ADV TDS.1, ALC FLR.1, AVA VAN.2, and AVA SCU EXT.1. AVA SCU EXT.1 is defined in Chapter 6.

This PP requires strict conformance of the ST or PP claiming conformance to this PP.

This PP satisfies the following Assurance Families: APE\_CCL.1, APE\_ECD.1, APE\_INT.1, APE OBJ.2, APE REQ.2 and APE SPD.1.

## 3 Security problem definition

### 3.1 Assets

The TOE protects following assets 'As.'

As.SCU Integrity of security services provided for the application software.

As.ConfUD Confidentiality of user data that requires confidentiality.

As.IntegUD Integrity of user data that requires integrity.

The TOE protects confidentiality of TSF data by the self-protection function of the hardware. The TOE protects user data that exists in non-volatile memory by the cryptographic function of the TOE.

User data may include user keys (a private key for digital signature generation of data, a private key for device authentication, a public key for verification of the application software a public key for certificate verification data, and so on), certificate, data exchanged via the software gate API, and the application software. The TOE cannot determine the necessary confidentiality and integrity of user data. Therefore, the user must securely store the user data that requires confidentiality and integrity by using the TOE function.

TSF data are an HGK, a key for decrypting user keys in the key storage, data for verification of the integrity of the key storage, data for verification of the integrity of the software gate, an IV, internal state transition data, and a chip ID.

### 3.2 Threats

### T.Internal\_Access

An attacker may attempt to tamper with the application software or the software gate and then use the TOE's cryptographic functions without permission to disclose or modify the user data.

Rationale: Following SFRs prevent modified application software or modified software gate from accessing the hardware inside the TOE to use the TOE's cryptographic functions.

- FDP\_IFC.1/API, FDP\_IFF.1/API specifies requirements for operating cryptographic functions by the application software that is an external entity. Only when the state transition of data of the software gate is verified, data is output from the cryptographic function to the external entity. That is, only the correct use of the cryptographic function is accepted.

- FDP\_MFW\_EXT.1 is called by FPT\_TST.1 to verify the integrity and, if needed, authenticity of the application software at startup.

- FPT\_TST.1 defines the verification of the integrity of the software gate at startup and supports the validation of the state transition data of the software gate by FDP IFC.1/API and FDP IFF.1/API.

- FPT\_FLS.1/SG maintains a secure state even if the integrity of the state transition of data of the software gate is compromised.

- FPT\_FLS.1/SB maintains a secure state even if the integrity of the software gate and application software and, if needed, authenticity of the application software is compromised at startup.

### T.Weak\_Import

An attacker may abuse the key storage import function to disclose or tamper with user data.

Rationale: According to the following SFRs, importing of the key storage with encrypted integrity verification data attached and integrity verification are performed to prevent the import of unauthorized user data.

- FDP\_IFC.1/Import, FDP\_IFF.1/Import specifies the requirements for operating the import functions by the application software that is an external entity. Only when the state transition of data of the software gate is verified can the user data be stored in the key storage via the import function. That is, only the correct use of the import function is accepted.

- FDP UIT.1 verifies the integrity of user data to be imported into key storage.

#### T.Unauthorized Update

An attacker may install unauthorized application software on the TOE to expose user data of the embedded device or disrupt the device's services. Alternatively, an attacker may illegally roll back to a version with a security failure to disclose the user data of the embedded device or disrupt embedded device services.

Rationale: According to the following SFRs, the TSF obtains the correct version of the application software, updates the application software, and verifies the updated application software.

- FPT\_TUD\_EXT.1 queries the application software for its current version, triggers the update, and verifies the updated application software before installation.

- FPT RPL.1 prevents rollback attempts.

- FPT\_FLS.1/UD preserves a secure state when an integrity or authenticity error of the application software occurs.

#### T.Weak Crypto

An attacker may disclose or alter the user data by exploiting improperly selected encryption algorithms, key generation method, key lengths, key destruction method, or an RBG.

Rationale: The TOE counters this threat by implementing an RBG with a sufficient entropy source and cryptographic algorithms with sufficient key length on the basis of an approved standard, and providing it to the application software, as defined in the following SFRs.

- (Option) FCS CKM.1/AK generates asymmetric keys.

- (Option) FCS CKM.1/SK generates symmetric keys.

- (Option) FCS\_CKM.4 ensures that keys and key materials in the volatile memory are destroyed in such a way as to prevent future recovery.

- (Selection) FCS COP.1/SKC encrypts and decrypts using symmetric key algorithms.

- (Selection) FCS\_COP.1/KeyEnc performs key encryption and decryption.

- (Selection) FCS\_COP.1/Hash uses hashing mechanisms.

- (Selection) FCS COP.1/MAC calculates MAC.

- (Option) FCS COP.1/SigGen generates digital signatures.

- (Selection) FCS COP.1/SigVer verifies digital signatures.

- (Selection) FCS\_KDF\_EXT.1 performs key derivation.

- (Selection) FCS RBG EXT.1 performs random bit generation.

• (Selection) FCS\_SNI\_EXT.1 ensures that the salt, nonce, and initialisation vector used by the TOE do not adversely affect key strength.

#### T.Leak Inherent

An attacker may expose the user data or TSF data like SCU's cryptographic keys by observing and analyzing changes in the TOE's power consumption during cryptographic operations.

Rationale: It mitigates leakage of unnecessary information to radiated electromagnetic waves and power consumption when SCU processes user and TSF data, making it difficult for attackers to expose useful data by performing statistical processing.

• FPT EMS EXT.1 mitigates the leakage of user data and TSF data from the TOE.

#### **T.Phys Probing**

By physically probing the inside of the TOE, an attacker may expose or modify the user data of the TOE like cryptographic keys, or other TSF data that is useful for other attacks.

Rationale: The following SFRs are to counter this threat of modifying or acquiring the user data by using equipment used for semiconductor analysis to photograph a memory cell or physically contact the inside of the TOE.

- FPT PHP.3 counters physical probing.

- FCS STG EXT.1 implements key storage outside the SCU.

- FCS\_STG\_EXT.2 uses cryptography to ensure confidentiality of the key storage outside the SCU.

- FCS STG EXT.3 uses cryptography to ensure integrity of the key storage outside the SCU.

#### T.Phys\_Manipulation

An attacker may modify the user data and encryption keys stored in the cryptographic function by physically manipulating the inside of the TOE or modify the security mechanism of the TOE for other attacks.

Rationale: The following SFRs are aimed at countering this threat that directly alters information assets or uses them as a stepping stone for other attacks by conducting physical operations inside the TOE.

- FPT PHP.3 counters physical tampering.

- FCS STG EXT.1 maintains key storage outside the SCU.

- FCS STG EXT.2 uses cryptography to ensure confidentiality of the key storage outside the SCU.

- FCS\_STG\_EXT.3 uses cryptography to ensure integrity of the key storage outside the SCU.

## 3.3 Organizational security policy

There is no organizational security policy.

## 3.4 Assumptions

#### A.Trusted User

The embedded device developer appropriately protects data stored outside the TOE.

The security objective for the operational environment is OE.Trusted User.

## 4 Security objectives

This chapter describes only security objectives for the operational environment in accordance with ASE OBJ.1.

## 4.1 Security objectives for the operational environment

## OE.Trusted\_User

The embedded device developer follows the guidance of the TOE regarding the protection of data held outside the TOE.

Rationale: This assumption is fulfilled if the embedded device developer implements protection of data held outside the TOE in accordance with the guidance of the TOE.

## 5 Security requirements

The conventions used in the SFR descriptions are as follows:

- (1) Unaltered SFRs are stated in the form used in [CC2] or their Extended Component Definition (ECD).

- (2) Refinement made in the PP: the added/removed text is indicated with **bold text**/strikethroughs. When text is substituted, the description will result in an additional description in bold.

- (3) Selections:

- a) Wholly or partially completed in the PP: the selection values (i.e., the selection values adopted in the PP or the remaining ones available for the ST) are indicated with <u>underlined text.</u>

- E.g., ECD [selection: physical, non-physical true, deterministic, hybrid physical, hybrid deterministic] might become [physical] (completion) or [selection: physical, non-physical true] (partial completion) in the PP.

- b) A number of SFRs include selections that determine or constrain other assignments or selections. In these cases, a table follows the requirement in which each row of the table defines a permitted set of choices. Each row includes a unique identifier defined solely to provide a label for the selection set.

- (4) Assignment wholly or partially completed in the PP: indicated with *italicized text*.

- (5) Assignment completed within a selection in the PP: the completed assignment text is indicated with *italicized and underlined text*.

- E.g., "[selection: change\_default, query, modify, delete, [assignment: other operations]]" in [CC2] or an ECD might become "[change\_default, [select\_tag]]" (completion of both selection and assignment) in the PP:

- (6) Iteration: indicated by adding a string starting with "/" (e.g., "FCS COP.1/Hash").

- (7) Extended SFRs and an SAR are identified by having a label 'EXT' at the end of the name.

## 5.1 Security functional requirements

## 5.1.1 Cryptographic support

### FCS STG EXT.1 Secure key storage

Hierarchical to: No other components

Dependencies: No dependencies

FCS\_STG\_EXT.1.1 The TSF shall provide [<u>software-based</u>] secure key storage for asymmetric private keys and [selection: <u>symmetric keys</u>, <u>secrets</u>, <u>no other keys</u>].

**FCS\_STG\_EXT.1.2** The TSF shall support the capability of importing keys/secrets into the TOE upon request of [the application software].

**FCS\_STG\_EXT.1.3** The TSF shall be capable of destroying keys/secrets in the secure key storage upon request of [the application software].

Application Note 1

The secure key storage is implemented in software in the memory inside the TOE, so this requirement covers it.

## FCS STG EXT.2 Key storage encryption

Hierarchical to: No other components

Dependencies: FCS COP.1

FCS\_STG\_EXT.2.1 The TSF shall protect the confidentiality of [all software-based key storage] using the following method: [assignment: as specified in FCS\_COP.1/KeyEnc].

Application Note 2

The ST author selects an SFR from Chapter 7 t70 decrypt the key storage. When re-encrypting, the ST author selects SFRs to encrypt and decrypt from Chapter 7.

### FCS STG EXT.3 Key integrity protection

Hierarchical to: No other components

Dependencies: FCS COP.1

**FCS\_STG\_EXT.3.1** The TSF shall protect the integrity of [all software-based key storage] by using [selection:

- A hash of the stored key in accordance with FCS\_COP.1/Hash [selection: SHA-256, SHA-384, SHA-512, SHA3-224, SHA3-256, SHA3-384, SHA3-512];

- A MAC of the stored key in accordance with FCS\_COP.1/MAC [selection: HMAC-SHA-1, HMAC-SHA-256, HMAC-SHA-384, HMAC-SHA-512, CMAC-AES-128, CMAC-AES-256];

- Symmetric key encryption in accordance with FCS\_COP.1/SKC [selection: AES\_CCM, AES\_GCM, AES\_KWP, AES\_KW];

- A digital signature of the stored key in accordance with FCS\_COP.1/SigVer using an asymmetric key that is protected in accordance with FCS\_STG\_EXT.2

Application Note 3

]

The ST author selects an SFR from Chapter 7 to protect the integrity of the key storage.

### 5.1.2 User data protection

## FDP IFC.1/API Subset information flow control (API)

Hierarchical to: No other components.

Dependencies: FDP IFF.1 Simple security attributes

**FDP\_IFC.1.1/API** The TSF shall enforce the [embedded device information flow control SFP] on [subject: cryptographic functions of the TOE, information: API call for the subject and API response from the subject, and operations: input to the API, execution of cryptographic functions and output from the API response].

#### FDP IFC.1/Import Subset information flow control (Import)

Hierarchical to: No other components.

Dependencies: FDP IFF.1 Simple security attributes

**FDP\_IFC.1.1/Import** The TSF shall enforce the [import information flow control SFP] on [subject: non-volatile memory of the TOE, information: the key storage, and operations: import].

## FDP IFF.1/API Simple security attributes (API)

Hierarchical to: No other components.

Dependencies: FDP IFC.1 Subset information flow control, FMT MSA.3 Static attribute initialisation

**FDP\_IFF.1.1/API** The TSF shall enforce the [embedded device information flow control SFP] on the basis of the following types of subject and information security attributes: [subject: cryptographic functions of the TOE, information: software gate API call for the subject and software gate API response from the subject, the security attributes of the subject: Internal state transition data to verify the integrity of pre-built software gate API calls, the security attribute of the information: Internal state transition results provided to the function that verifies the integrity of software gate API calls].

**FDP\_IFF.1.2/API** The TSF shall permit an information flow between a controlled subject and information via a controlled operation if the following rules hold: [permits the information flow of software gate API calls to the subject and software gate API responses from the subject, that is, the output of cryptographic operations, only when the internal state transition data and result calculated by TSF match and the integrity verification of the software gate API call is successful].

**FDP\_IFF.1.4**/**API** The TSF shall explicitly authorize an information flow on the basis of the following rules: [No rules, based on security attributes that explicitly authorize information flows].

**FDP\_IFF.1.5**/**API** The TSF shall explicitly deny an information flow on the basis of the following rules: [No rules, based on security attributes that explicitly deny information flows].

Application Note 4

The information security attribute is a value calculate for each software gate API call, and the TSF compares the value with reference data to verify authenticity. If a cryptographic algorithm is used for the method of computing the internal state transitions to verify integrity, the implemented algorithm should be selected from Chapter 7.

If the pre-built internal state transition data is to be protected by cryptography, the implemented algorithm should be selected from Chapter 7.

### FDP IFF.1/Import Simple security attributes (Import)

Hierarchical to: No other components.

Dependencies: FDP IFC.1 Subset information flow control, FMT MSA.3 Static attribute initialisation

**FDP\_IFF.1.1/Import** The TSF shall enforce the [import information flow control SFP] on the basis of the following types of subject and information security attributes: [subject: non-volatile memory of the TOE, information: the key storage, the security attributes of the subject: none, the security attribute of the information: value used to verify the integrity of the key storage.].

**FDP\_IFF.1.2/Import** The TSF shall permit an information flow between a controlled subject and information via a controlled operation if the following rules hold:

enables the import of the key storage into the subject only when the value used to verify the integrity of the key storage matches that calculated by the TSF to verify the integrity of the key storage.].

**FDP\_IFF.1.4/Import** The TSF shall explicitly authorize an information flow on the basis of the following rules: [No rules, based on security attributes that explicitly authorize information flows].

**FDP\_IFF.1.5/Import** The TSF shall explicitly deny an information flow on the basis of the following rules: [No rules, based on security attributes that explicitly deny information flows].

Application Note 5

The ST author selects an SFR from Chapter 7 to verify the integrity. The selections are hashes in accordance with FCS\_COP.1/Hash, a MAC in accordance with FCS\_COP.1/MAC, and authenticated encryption in accordance with FCS\_COP.1/SKC.

#### FDP MFW EXT.1 Basic software integrity and authenticity (Secure boot)

Hierarchical to: No other components

Dependencies: FCS COP.1

FDP MFW EXT.1.1 The TSF shall have the ability to verify [the integrity] of the application software.

**FDP\_MFW\_EXT.1.2** The TSF shall provide a capability to generate evidence of [the <u>integrity</u>] of **the application software**.

Application Note 6

The TOE ensures the integrity of the application software (Secure boot). The ST author selects an SFR from Chapter 7 to verify the integrity. The selections are hashes in accordance with FCS\_COP.1/Hash, a MAC in accordance with FCS\_COP.1/MAC, and authenticated encryption in accordance with FCS\_COP.1/SKC.

#### FDP UIT.1 Data exchange integrity

Hierarchical to: No other components.

Dependencies: [FDP\_ACC.1 Subset access control, or FDP\_IFC.1 Subset information flow control] [FTP\_ITC.1 Inter-TSF trusted channel, or FTP\_TRP.1 Trusted path]

**FDP\_UIT.1.1** The TSF shall enforce the [*import information flow control SFP*] to [*receive*] user data in a manner protected from [*modification*] errors.

**FDP** UIT.1.2 The TSF shall determine on receipt of user data whether [modification] has occurred.

Application Note 7

The TOE ensures the integrity of the application software (Secure boot). The ST author selects an SFR from Chapter 7 to verify the integrity. The selections are hashes in accordance with FCS\_COP.1/Hash, a MAC in accordance with FCS\_COP.1/MAC, and authenticated encryption in accordance with FCS\_COP.1/SKC.

#### **5.1.3** Protection of the TSF

### FPT EMS EXT.1 Mitigation of leak from the TOE

Hierarchical to: No other components

Dependencies: No dependencies

**FPT\_EMS\_EXT.1** The TOE shall not emit [power consumption, electromagnetic emanation] over its [power line of the TOE, surface of the TOE] in such an amount that these emissions enable access to [list of type of TSF data as follows] and [list of type of user data as follows].

Table 5-1 Data to protect against side-channel attacks

| list of type of TSF data                                          | list of type of user data             |

|-------------------------------------------------------------------|---------------------------------------|

| An encryption key of the key storage [assignment: other TSF data] | assignment: list of type of user data |

## FPT FLS.1/SB Failure with preservation of secure state (Secure boot)

Hierarchical to: No other components

Dependencies: No dependencies

**FPT\_FLS.1.1/SB** The TSF shall preserve a secure state when the following types of failures occur: [software gate integrity violation at startup, application software integrity violation at startup, [selection: application authenticity violation at startup, [assignment: other violation]]].

Application Note 8

This SFR maintains a secure state when failure of the verification of the software gate and application software by FPT TST.1 occurs.

## FPT FLS.1/SG Failure with preservation of secure state (Software gate)

Hierarchical to: No other components

Dependencies: No dependencies

**FPT\_FLS.1.1/SG** The TSF shall preserve a secure state when the following types of failures occur: [failure of internal transition data integrity verification as specified in FPT\_TST.1].

Application Note 9

This SFR covers the case where a mismatch occurs between the internal state transition data initiated by FPT\_TST.1 and the calculated one.

### FPT FLS.1/UD Failure with Preservation of Secure State (Trusted update)

Hierarchical to: No other components

Dependencies: No dependencies

**FPT\_FLS.1.1/UD** The TSF shall preserve a secure state when the following types of failures occur: [integrity or authenticity error of the application software for update].

Application Note 10

This requirement is intended to verify the integrity and authenticity of the application software being updated.

### FPT PHP.3 Resistance to physical attack

Hierarchical to: No other components

Dependencies: No dependencies

**FPT\_PHP.3.1** The TSF shall resist [physical manipulation and probing] to the [TSF] by responding automatically such that the SFRs are always enforced.

Refinement: The TSF will implement appropriate mechanisms to continuously counter physical manipulation and probing. Due to the nature of these attacks (especially manipulation) the TSF can by no means detect attacks on all of its elements. Therefore, permanent protection against these attacks is required to ensure that SFRs are enforced. Hence, "automatic response" indicates (i) the assumption that there might be an attack at any time and (ii) countermeasures are provided at any time.

Application Note 11

The ST shall describe the automatic response of the TOE. The SFRs are enforced if the TOE stops operation or does not operate at all if a physical manipulation or probing attack is detected and the security cannot be ensured in another way.

## FPT\_RPL.1 Replay detection (rollback)

Hierarchical to: No other components

Dependencies: No dependencies

**FPT\_RPL.1.1** The TSF shall detect replay for the following entities: [application software of a previous version].

**FPT\_RPL.1.2** The TSF shall [prevent the execution of the loaded application software and perform [selection, choose one of: [assignment: other actions], no other actions]] when replay is detected.

Application Note 12

When loading application software is requested, the TSF ensures that the verified application software version is equal to or higher than the previously verified version. Loading an older application software version could expose known vulnerabilities.

#### FPT TST.1 TSF testing

Hierarchical to: No other components

Dependencies: No dependencies

**FPT\_TST.1.1** The TSF shall run a suite of self-tests *during initial startup*, [selection: periodically during normal operation, at the request of **the application software**, at the conditions [assignment: conditions under which self-test should occur] to demonstrate the correct operation of [the cryptographic functions].

**FPT\_TST.1.2** The TSF shall provide **the hardware gate** with the capability to verify the integrity of [<u>the</u> internal state transition data].

**FPT\_TST.1.3** The TSF shall provide **the self-test during initial startup** with the capability to verify the integrity of [*the software gate*].

Application Note 13

The purpose of this requirement is to verify the completeness of the state transitions by matching the internal state transition results with the internal state transition data, so that the verification of the software gate itself can be performed. Self-testing during initial commissioning verifies the integrity of the software gate, the integrity of the application software, and optionally the authenticity (Secure boot). The TOE ensures the integrity of the application software (Secure boot). The ST author selects an SFR from Chapter 7 to verify the software gate integrity. The

selections are stored hashes in accordance with FCS\_COP.1/Hash, a MAC in accordance with FCS\_COP.1/MAC, authenticated encryption in accordance with FCS\_COP.1/SKC, and signature verification in accordance with FCS\_COP.1/SigVer.

## FPT TUD EXT.1 Trusted update

Hierarchical to: No other components

Dependencies: FCS COP.1

**FPT\_TUD\_EXT.1.1** The TSF shall provide [the software gate] the ability to query the current version of **the application software**.

**FPT\_TUD\_EXT.1.2** The TSF shall provide [*the software gate*] the ability to initiate updates to **the application software**.

**FPT\_TUD\_EXT.1.3** The TSF shall verify updates to **the application software** using a [selection: <u>digital signature in accordance with FCS\_COP.1/SigVer</u>, <u>a MAC in accordance with FCS\_COP.1/MAC</u>] prior to installing those updates.

Application Note 14

This requirement provides the ability for the TOE to update the application software. The TOE shall ensure the integrity and authenticity of the application software by verifying the application software to be updated upon update. The ST author selects the algorithm to be implemented from Chapter 7.

## 5.2 Security assurance requirements

The SARs defined in this PP are EAL 1 + ASE\_SPD.1 + ADV\_ARC.1 + ADV\_FSP.2 + ADV\_TDS.1 + ALC FLR.1 + AVA VAN.2 + AVA SCU EXT.1.

## 5.3 Security requirements rationale

#### 5.3.1 Security functional requirements rationale

Table 5-2 shows the dependencies satisfied in the SFRs of baseline requirements.

Application Note 15

If selection-based SFRs are selected, the ST author shall indicate the dependencies that will be met and describe the rationale for any dependencies that will not be met.

If option-based SFRs are added, the ST author shall indicate the dependencies that will be met and describe the rationale for any dependencies that will not be met.

| Requirements     | CC dependencies | Satisfied dependencies           |

|------------------|-----------------|----------------------------------|

| FCS_STG_EXT.1    | No dependency   | NA                               |

| FCS_STG_EXT.2    | FCS_COP.1       | Note: The ST author selects SFR. |

| FCS_STG_EXT.3    | FCS_COP.1       | Note: The ST author selects SFR. |

| FDP_IFC.1/API    | FDP_IFF.1       | FDP_IFF.1/API                    |

| FDP_IFC.1/Import | FDP_IFF.1       | FDP_IFF.1/Import                 |

Table 5-2 Baseline security functional requirements

| Requirements     | CC dependencies              | Satisfied dependencies                         |

|------------------|------------------------------|------------------------------------------------|

| FDP_IFF.1/API    | FDP_IFC.1 and FMT_MSA.3      | FDP_IFC.1/API                                  |

|                  |                              | Note: FMT_MSA.3 is not satisfied.              |

| FDP_IFF.1/Import | FDP_IFC.1 and FMT_MSA.3      | FDP_IFC.1/Import                               |

|                  |                              | Note: FMT_MSA.3 is not satisfied.              |

| FDP_MFW_EXT.1    | FCS_COP.1                    | Note: The ST author selects SFR.               |

| FDP_UIT.1        | [FDP_ACC.1 or FDP_IFC.1] and | FDP_IFC.1/Import                               |

|                  | [FTP_ITC.1 or FTP_TRP.1]     | Note: FTP_ITC.1 or FTP_TRP.1 is not satisfied. |

| FPT_EMS_EXT.1    | No dependency                | NA                                             |

| FPT_FLS.1/SB     | No dependency                | NA                                             |

| FPT_FLS.1/SG     | No dependency                | NA                                             |

| FPT_FLS.1/UD     | No dependency                | NA                                             |

| FPT_PHP.3        | No dependency                | NA                                             |

| FPT_RPL.1        | No dependency                | NA                                             |

| FPT_TST.1        | No dependency                | NA                                             |

| FPT_TUD_EXT.1    | FCS_COP.1                    | Note: The ST author selects SFR.               |

The dependency FCS\_COP.1 of FCS\_STG\_EXT.2, FCS\_STG\_EXT.3, FDP\_MFW\_EXT.1, and FPT\_TUD\_EXT.1 are to be filled in by the ST author, selected from the selection-based requirements of the cryptographic functional requirements that are being used.

The dependency FMT\_MSA.3 of FDP\_IFF.1/API is not satisfied. FMT\_MSA.3 defines the management of "a security attribute of information." In this TOE, this attribute is an API attribute that is calculated each time an API is called and is not managed by the TOE. Thus, FMT\_MSA.3 is not applicable.

The dependency FMT\_MSA.3 of FDP\_IFF.1/Import is not satisfied. FMT\_MSA.3 defines the management of "a security attribute of information." In this TOE, this attribute is calculated outside of the TOE and is not managed by the TOE. Thus, FMT MSA.3 is not applicable.

The dependency FTP\_ITC.1 or FTP\_TRP.1 of FDP\_UIT.1 is not satisfied. The user data encrypted and MAC granted outside the TOE is imported, so the trusted path/trusted channel is not applied.

#### 5.3.2 Security assurance requirements rationale

Security assurance requirements applied for the TOE are EAL1 + ASE\_SPD.1 + ADV\_ARC.1 + ADV\_FSP.2 + ADV\_TDS.1 + ALC\_FLR.1 + AVA\_VAN.2 and AVA\_SCU\_EXT.1. Extended security functional requirement AVA\_SCU\_EXT.1 is defined in Chapter 6.

Considering the value of the assets handled by the TOE and the operating environment in which the TOE is used, the decision to select these SARs was derived from being able to withstand the attacks of an attacker with basic attack potential (i.e., AVA\_VAN.1 or AVA\_VAN.2). Next, by considering the characteristics of the TOE where it is used for inexpensive devices, the level required for developers should be needed to obtain appropriate assurance while reducing the cost and time required for an evaluation and a certification.

However, the higher AVA\_VAN.2 is selected because it can withstand the attacks of an attacker with basic attack potential (i.e., AVA\_VAN.1 or AVA\_VAN.2) and because of its dependencies ADV\_ARC.1, ADV FSP.2, and ADV TDS.1 are selected. In addition to searching for known vulnerabilities, a meaningful

assurance of EAL1 or higher is obtained by performing a vulnerability analysis on the basis of the provided evaluation documentation, and independent testing based on the TOE specification.

In addition, it is impossible not to use configuration management, mass production, and logistics systems in recent semiconductor and embedded systems development, and from this perspective, the ALC class is the minimum to be included in EAL1. ALC\_FLR.1 has also been added, and it is hoped that the TOE will be maintained in the future by tracking and correcting security flaws found by the developers. ASE\_SPD.1 has been added to help the ST readers understand the use cases envisioned by the PP, threats, and assumptions associated with them.

#### AVA SCU EXT.1 Vulnerability survey of the SCU

The TOE is a hardware product that controls the cryptographic engine and hardware gate through the software gate. Although it is a microcontroller, this TOE does not handle high-value assets like microcontrollers for smart cards, and it is assumed that the asset value handled is low. Therefore, it is assumed that the attacker assumed in this TOE has a lower attack potential than one who attacks the smart card microcontroller.

In the evaluation by the Common Criteria, it is mandatory to apply [AAPS] to the vulnerability assessment of smart cards and similar devices. For this reason, a new extended assurance component AVA\_SCU\_EXT has been newly defined on the basis of [PPTEE], and the attack should be noted by the SCU developer and TOE developer who use the SCU, and an attack potential calculation table for hardware attacks based on the SOG-IS support document [AAPS] are defined. See Chapter 9 for AVA SCU EXT.

Table 5-3 shows the dependencies satisfied in the SARs of this TOE. As shown, all dependencies of the selected SARs are satisfied.

| Requirements | CC dependencies                 | Satisfied dependencies          |

|--------------|---------------------------------|---------------------------------|

| ASE_CCL.1    | ASE_ECD.1, ASE_INT.1, ASE_REQ.1 | ASE_ECD.1, ASE_INT.1, ASE_REQ.1 |

| ASE_ECD.1    | No dependency                   | NA                              |

| ASE_INT.1    | No dependency                   | NA                              |

| ASE_OBJ.1    | No dependency                   | NA                              |

| ASE_REQ.1    | ASE_ECD.1                       | ASE_ECD.1                       |

| ASE_SPD.1    | No dependency                   | NA                              |

| ASE_TSS.1    | ASE_INT.1, ASE_REQ.1, ADV_FSP.1 | ADV_FSP.2                       |

| ADV_ARC.1    | ADV_FSP.1, ADV_TDS.1            | ADV_FSP.2, ADV_TDS.1            |

| ADV_FSP.2    | ADV_TDS.1                       | ADV_TDS.1                       |

| ADV_TDS.1    | ADV_FSP.2                       | ADV_FSP.2                       |

| AGD_OPE.1    | ADV_FSP.1                       | ADV_FSP.2                       |