FIPS 140-2 Security Policy Document Revision: 1.0

H/W version: MZILT800HAHQ-000C9, MZILT960HAHQ-000C9, MZILT960HAHQ-00AC9, MZILT1T6HAJQ-000C9, MZILT1T9HAJQ-000C9, MZILT1T9HAJQ-00AC9, MZILT3T8HALS-000C9, MZILT3T8HALS-00AC9, MZILT3T8HALS-00AC9, MZILT3THMLA-00AC9, MZILT15THMLA-00AC9, MZILT15THMLA-00AC9, MZILT15THMLA-00AC9, MZILT3THMLA-00OC9

F/W version: EXF3, EXV3, EXF5, EXV5 and EZF5

# **Revision History**

| Author(s)    | Version | Updates         |

|--------------|---------|-----------------|

| Seungjae Lee | 1.0     | Initial Version |

# **Table of Contents**

| 1.  | Introduction                                                         | 4              |

|-----|----------------------------------------------------------------------|----------------|

|     | 1.1. Hardware and Physical Cryptographic Boundary                    |                |

|     | 1.2. Firmware and Logical Cryptographic Boundary                     |                |

| 2.  | Acronym                                                              |                |

| 3.  | Security Level Specification                                         |                |

| 4.  | Cryptographic Functionality                                          | 22             |

|     | 4.1. Approved algorithms                                             |                |

|     | 4.2. Non-Approved Algorithm                                          | 23             |

|     | 4.3. Critical Security Parameters                                    | 24             |

|     | 4.4. Public Security Parameters                                      |                |

| 5.  | Physical Ports and Logical Interfaces                                | 2 <del>6</del> |

| 6.  | Roles, Services and Authentication                                   |                |

|     | 6.1. Roles                                                           | 27             |

|     | 6.2. Authentication                                                  | 28             |

|     | 6.3. Services                                                        | 29             |

|     | 6.3.1. Authenticated Services                                        | 29             |

|     | Unauthenticated Services                                             | 30             |

| 7.  | Physical security policy                                             | 31             |

| 8.  | Electromagnetic Interference/Electromagnetic Compatibility (EMI/EMC) |                |

| 9.  | Mitigation of Other Attacks Policy                                   |                |

| 10. | Security rules                                                       | 37             |

|     | 10.1. Secure Installation                                            | 37             |

|     | 10.2. Operational description of Module                              | 38             |

|     | 10.3. Power-on Self-Tests                                            | 39             |

## 1. Introduction

Samsung Electronics Co., Ltd. ("Samsung") SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, herein after referred to as a "cryptographic module" or "module", SSD (Solid State Drive), satisfies all applicable FIPS 140-2 Security Level 2 requirements, supporting TCG Opal SSC based SED (Self-Encrypting Drive) features, designed to protect unauthorized access to the user data stored in its NAND Flash memories. The built-in AES HW engines in the cryptographic module's controller provide on-the-fly encryption and decryption of the user data without performance loss. The SED's nature also provides instantaneous sanitization of the user data via cryptographic erase.

| Module Name                        | Hardware Version   | Firmware<br>Version | Drive<br>Capacity |

|------------------------------------|--------------------|---------------------|-------------------|

|                                    | MZILT960HAHQ-000C9 |                     | 960GB             |

|                                    | MZILT960HAHQ-00AC9 |                     | 90000             |

|                                    | MZILT1T9HAJQ-000C9 | EXF3/EXF5           | 1.9TB             |

|                                    | MZILT1T9HAJQ-00AC9 | EAF5/EAF5           |                   |

| Samsung SAS 12G TCG Enterprise SSC | MZILT3T8HALS-000C9 | EXV3/EXV5           | 3.8TB             |

| SEDs PM1643                        | MZILT3T8HALS-00AC9 |                     |                   |

| SEDS PIVITO45                      | MZILT7T6HMLA-000C9 |                     | 7.6TB             |

|                                    | MZILT7T6HMLA-00AC9 |                     | 7.016             |

|                                    | MZILT15THMLA-000C9 |                     | 15.3TB            |

|                                    | MZILT15THMLA-00AC9 |                     | 13.315            |

|                                    | MZILT30THMLA-000C9 | EXV5                | 30.7TB            |

| Samsung SAS 12G TCG Enterprise SSC | MZILT800HAHQ-000C9 |                     | 800GB             |

|                                    | MZILT1T6HAJQ-000C9 | EZF5                | 1.6TB             |

| SEDs PM1645                        | MZILT3T2HALS-000C9 |                     | 3.2TB             |

<u>Exhibit 1</u> – Versions of Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series.

#### 1.1. Hardware and Physical Cryptographic Boundary

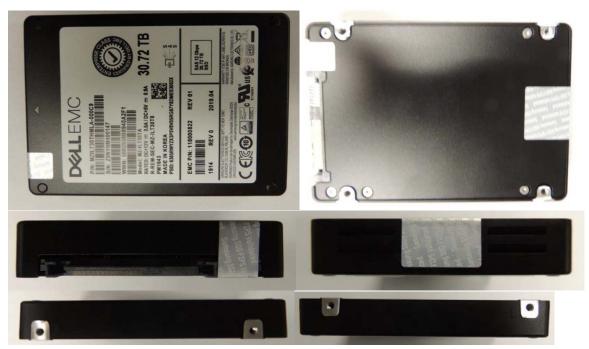

The following photographs show the cryptographic module's top and bottom views. The multiple-chip standalone cryptographic module consists of hardware and firmware components that are all enclosed in two aluminum alloy cases, which serve as the cryptographic boundary of the module. The top and bottom cases are assembled by screws and the tamper-evident labels are applied for the detection of any opening of the cases. No security relevant component can be seen within the visible spectrum through the opaque enclosure. New firmware versions within the scope of this validation must be validated through the FIPS 140-2 CMVP. Any other firmware loaded into this module is out of the scope of this validation and requires a separate FIPS 140-2 validation.

<u>Exhibit 2</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT960HAHQ-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

Exhibit 3 – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT960HAHQ-00AC9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 4</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT1T9HAJQ-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 5</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT1T9HAJQ-00AC9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 6</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT3T8HALS-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 7</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT3T8HALS-00AC9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 8</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT7T6HMLA-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

Exhibit 9 – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT7T6HMLA-00AC9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 10</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT15THMLA-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

Exhibit 11 – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT15THMLA-00AC9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 12</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT30THMLA-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

Exhibit 13 – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT800HAHQ-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

Exhibit 14 – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT1T6HAJQ-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

<u>Exhibit 15</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series, MZILT3T2HALS-000C9, Cryptographic Boundary (From top to bottom – Left to right: top side, bottom side, front side, back side, left side, and right side).

## 1.2. Firmware and Logical Cryptographic Boundary

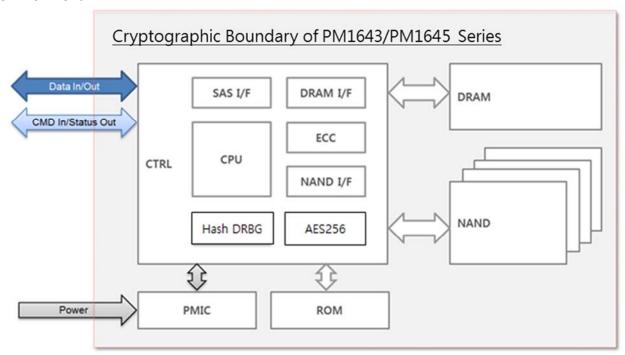

The PM1643/PM1645 series use a single ship controller with a SAS interface on the system side and Samsung NAND flash internally. The following figure depicts the Module operational environment.

<u>Exhibit 16</u> – Block Diagram for Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series.

# 2. Acronym

| Acronym  | Description                                  |

|----------|----------------------------------------------|

| CTRL     | RFX Controller                               |

|          | (SAMSUNG RFX SAS 12G TLC/MLC SSD Controller) |

| SAS I/F  | Serial Attached SCSI Interface               |

| CPU      | Central Processing Unit (ARM-based)          |

| DRAM I/F | Dynamic Random Access Memory Interface       |

| ECC      | Error Correcting Code                        |

| NAND I/F | NAND Flash Interface                         |

| PMIC     | Power Management Integrated Circuit          |

| ROM      | Read-only Memory                             |

| DRAM     | Dynamic Random Access Memory                 |

| NAND     | NAND Flash Memory                            |

| LBA      | Logical Block Address                        |

| MEK      | Media Encryption Key                         |

| MSID     | Manufactured SID(Security Identifier)        |

Exhibit 17 – Acronym and Descriptions for Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series.

# 3. Security Level Specification

| Security Requirements Area                | Level |

|-------------------------------------------|-------|

| Cryptographic Module Specification        | 2     |

| Cryptographic Module Ports and Interfaces | 2     |

| Roles, Services, and Authentication       | 2     |

| Finite State Model                        | 2     |

| Physical Security                         | 2     |

| Operational Environment                   | N/A   |

| Cryptographic Key Management              | 2     |

| EMI/EMC                                   | 3     |

| Self-tests                                | 2     |

| Design Assurance                          | 2     |

| Mitigation of Other Attacks               | N/A   |

**Exhibit 18** – Security Level Table.

# 4. Cryptographic Functionality

# 4.1. Approved algorithms

The cryptographic module supports the following Approved algorithms for secure data storage:

| CAVP            | Algorith | Standard   | Mode /     | Key Lengths,     | Use                                                                                                                      |

|-----------------|----------|------------|------------|------------------|--------------------------------------------------------------------------------------------------------------------------|

| Cert.           | m        |            | Method     | Curves or Moduli |                                                                                                                          |

| #5240           | AES      | FIPS 197   | XTS        | 256-bit          | Data Encryption                                                                                                          |

|                 |          | SP 800-38E |            |                  | / Decryption                                                                                                             |

|                 |          |            |            |                  | Note: AES-ECB is the pre-requisite for AES-XTS; AES-ECB alone is NOT supported by the cryptographic module in FIPS Mode. |

| Vendor          | CKG      | SP800-133  |            |                  | Cryptographic                                                                                                            |

| Affirmed        |          |            |            |                  | Key Generation                                                                                                           |

| #1948           | DRBG     | SP 800-90A | Hash_ DRBG |                  | Deterministic                                                                                                            |

|                 |          | Revision 1 | (SHA-256)  |                  | Random Bit                                                                                                               |

|                 |          |            |            |                  | Generation                                                                                                               |

| #2785           | RSA      | FIPS 186-4 | SigVer     | PSS-2048         | Digital Signature<br>Verification                                                                                        |

| #4178,<br>#4179 | SHS      | FIPS 180-4 | SHA-256    |                  | Message Digest                                                                                                           |

<u>Exhibit 19 -</u> Samsung SAS 12G TCG Enterprise SSC SED PM1643/PM1645 Series Approved Algorithms.

NOTE 1: This module supports AES-XTS which is only approved for storage applications.

# 4.2. Non-Approved Algorithm

The cryptographic module supports the following non-Approved but allowed algorithms:

| Algorithm | Use                                                 |

|-----------|-----------------------------------------------------|

| NDRNG     | Non-deterministic Random Number Generator (only     |

|           | used for generating seed materials for the Approved |

|           | DRBG)                                               |

<u>Exhibit 20 -</u> Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series non-Approved but allowed algorithms.

# 4.3. Critical Security Parameters

The cryptographic module contains the following Keys and CSPs:

| 9 .                   | Generation, Storage and Zeroization              | C:               |

|-----------------------|--------------------------------------------------|------------------|

| CSPs                  | Methods                                          | Size             |

| DRBG Internal State   | Generation: SP 800-90A HASH_DRBG (SHA-256)       | V : 440-bits     |

|                       | Storage: Plaintext in DRAM                       | C: 440-bits      |

| Note: The values of V | Zeroization: "Initialization", "Erase an LBA     |                  |

| and C are the "secret | Range's Data" and "Zeroize" service              |                  |

| values" of the        |                                                  |                  |

| internal state.       |                                                  |                  |

| DRBG Seed             | Generation: via NDRNG                            | Entropy input    |

|                       | Storage: Plaintext in DRAM                       | String: 440-bits |

|                       | Zeroization: via "Initialization", "Erase an LBA | Nonce: 128-bits  |

|                       | Range's Data" and "Zeroize" service              | Personalization  |

|                       |                                                  | String: 512-bits |

| DRBG Entropy Input    | Generation: via NDRNG                            | 440-bits         |

| String                | Storage: Plaintext in DRAM                       |                  |

|                       | Zeroization: via "Initialization", "Erase an LBA |                  |

|                       | Range's Data" and "Zeroize" service              |                  |

| CO Password           | Generation: N/A                                  | 48-256 bits      |

|                       | Storage: Plaintext in Flash Memory and used in   |                  |

|                       | SRAM                                             |                  |

|                       | Zeroization: via "Initialization" and "Zeroize"  |                  |

| User Password         | service Generation: N/A                          | 48-256 bits      |

| USEI Password         | Storage: Plaintext in Flash Memory and used in   | 46-250 DILS      |

|                       | SRAM                                             |                  |

|                       | Zeroization: via "Initialization" and "Zeroize"  |                  |

|                       | service                                          |                  |

| MEK                   | Generation: SP 800-90A Hash_DRBG (SHA-256)       | 256-bits         |

|                       | As per SP 800-133 Section 7.1, key generation is |                  |

|                       | performed as per the "Direct Generation: of      |                  |

|                       | Symmetric Keys" which is an Approved key         |                  |

|                       | generation method                                |                  |

|                       | Key Type : AES-XTS 256                           |                  |

|                       | Storage: Plaintext in Flash Memory and used in   |                  |

|                       | SRAM                                             |                  |

|                       | Zeroization: via "Initialization", "Lock an LBA  |                  |

|                       | Range", "Erase an LBA Range's Data" and          |                  |

|                       | "Zeroize" service                                |                  |

Exhibit 21 – CSPs and details on Generation, Storage and Zeroization Methods.

NOTE 2: In accordance with FIPS 140-2 IG D.12, the cryptographic module performs Cryptographic Key Generation (CKG) as per SP 800-133 (Vendor Affirmed). The resulting generated symmetric key is the unmodified output from SP 800-90A DRBG.

## 4.4. Public Security Parameters

| Public Keys         | Generation, Storage and Zeroization Methods         |

|---------------------|-----------------------------------------------------|

| FW Verification Key | Generation: N/A                                     |

| (RSA Public Key)    | Key Type: RSA 2048-PSS                              |

|                     | Storage: Plaintext in Flash Memory and used in SRAM |

|                     | Zeroization: N/A                                    |

<u>Exhibit 22</u> – Public Keys and details on Generation, Storage and Zeroization Methods

# 5. Physical Ports and Logical Interfaces

| Physical Port | Logical Interface |

|---------------|-------------------|

|               | Data Input/Output |

| SAS Connector | Control Input     |

|               | Status Output     |

|               | Power Input       |

<u>Exhibit 23</u> – Specification of the Samsung SAS 12G TCG Enterprise SSC SEDs PM1643/PM1645 Series Cryptographic Module Physical Ports and Logical Interfaces.

# 6. Roles, Services and Authentication

#### **6.1.** Roles

The following table defines the roles, type of authentication, and associated authenticated data types supported by the cryptographic module:

| Role      | Authentication Data |

|-----------|---------------------|

| CO Role   | Password            |

| User Role | Password            |

| FW Loader | RSA                 |

Exhibit 24 - Roles and Required Identification and Authentication (FIPS 140-2 Table C1).

#### 6.2. Authentication

The authentication mechanism allows 6-byte length or longer (32-byte) Password, where each byte can be any of 0x00 to 0xFF, for every Cryptographic Officer and User role supported by the module, which means a single random attempt can succeed with the probability of  $1/2^{48}$  or lower.

Each authentication attempt takes at least 6ms and the number of attempts is limited to TryLimit, which is set to 5 in manufacturing time. Since the module takes at least 4 seconds to be ready after power-on and 5 authentication failures require a power-cycle, it takes 4030ms for every 5th authentication attempt. Therefore, the probability of multiple random attempts to succeed in one minute is  $75 / 2^{48}$ , which is much less than the FIPS 140-2 requirement 1/100,000.

The authentication mechanism for FW Loader role is RSA PSS-2048 with SHA256 digital signature verification, which means a single random attempt, can succeed with the probability of  $1/2^{112}$ .

Each RSA Signature Verification authentication attempt takes at least 50ms. So the number of attempts for one minute cannot exceed 1200((60\*1000)/50). Therefore, the probability of multiple random attempts to succeed in one minute is 1200/2<sup>112</sup>, which is much less than the FIPS 140-2 requirement 1/100,000.

| Authentication Mechanism                              | Strength of Mechanism                                                                                                                                                |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Password (Min: 6 bytes, Max: 32 bytes) Authentication | <ul> <li>Probability of 1/2<sup>48</sup> in a single random attempt</li> <li>Probability of 75/2<sup>48</sup> in multiple random attempts in a minute</li> </ul>     |

| RSA Signature Verification                            | <ul> <li>Probability of 1/2<sup>112</sup> in a single random attempt</li> <li>Probability of 1200/2<sup>112</sup> in multiple random attempts in a minute</li> </ul> |

<u>Exhibit 25</u> - Strengths of Authentication Mechanisms (FIPS 140-2 Table C2).

#### 6.3. Services

#### **6.3.1.** Authenticated Services

The following table lists roles, services, cryptographic keys, CSPs and Public Keys and the types of access that are available to each of the authorized roles via the corresponding services:

|               | Service                                | Countage which Kaus                         |      | Type(s) of Access |          |         |  |

|---------------|----------------------------------------|---------------------------------------------|------|-------------------|----------|---------|--|

| Role          |                                        | Cryptographic Keys,<br>CSPs and Public Keys | R=   | W=                | G=       | Z=      |  |

|               |                                        |                                             | Read | Write             | Generate | Zeroize |  |

|               |                                        | DRBG Internal State                         | О    |                   | 0        | О       |  |

|               |                                        | DRBG Seed                                   | О    |                   | 0        | 0       |  |

|               | Initialization                         | DRBG Entropy Input String                   | О    |                   | 0        | 0       |  |

|               |                                        | CO Password                                 |      | О                 |          | О       |  |

|               |                                        | MEK                                         |      |                   | 0        | О       |  |

|               | Drive Extended Status                  | N/A                                         |      | N/A               |          |         |  |

|               | Admin/User Authority<br>Enable/Disable | N/A                                         | N/A  |                   |          |         |  |

|               | Lock an LBA Range                      | MEK                                         |      |                   |          | 0       |  |

|               | Unlock an LBA Range                    | MEK                                         | 0    |                   |          |         |  |

| Cryptographic | Configure an LBA Range                 | N/A                                         | N/A  |                   |          |         |  |

| Officer       |                                        | DRBG Internal State                         | 0    |                   | 0        | 0       |  |

|               | Erase an LBA Range's<br>Data           | DRBG Seed                                   | 0    |                   | 0        | 0       |  |

|               |                                        | DRBG Entropy Input String                   | 0    |                   | О        | 0       |  |

|               |                                        | MEK                                         |      |                   | О        | 0       |  |

|               |                                        | User Password                               |      | О                 |          | 0       |  |

|               |                                        | DRBG Internal State                         |      |                   |          | 0       |  |

|               |                                        | DRBG Seed                                   |      |                   |          | O       |  |

|               | Zeroize                                | DRBG Entropy Input String                   |      |                   |          | O       |  |

|               | Zeroize                                | CO Password                                 |      |                   |          | 0       |  |

|               |                                        | User Password                               |      |                   |          | 0       |  |

|               |                                        | MEK                                         |      |                   |          | 0       |  |

| ·             | Unlock an LBA Range                    | MEK                                         | О    |                   |          |         |  |

| User          | Set User Password                      | User Password                               |      | 0                 |          |         |  |

| USCI          | Lock an LBA Range                      | MEK                                         |      |                   |          | O       |  |

|               | Configure an LBA Range                 | N/A                                         | N/A  |                   |          |         |  |

| FW Loader     | Update the firmware                    | FW Verification Key                         | O    |                   |          |         |  |

Exhibit 26 – Services Authorized for Roles, Access Rights within Services (FIPS 140-2 Table C3, Table C4).

#### **Unauthenticated Services**

The following table lists the unauthenticated services:

| Role                                            | Unauthenticated<br>Service | Cryptographic Keys & CSPs | Type(s) of Access |       |          |         |

|-------------------------------------------------|----------------------------|---------------------------|-------------------|-------|----------|---------|

|                                                 |                            |                           | R=                | W=    | G=       | Z=      |

|                                                 |                            |                           | Read              | Write | Generate | Zeroize |

| Cryptographic<br>Officer, User and<br>FW Loader | Zeroize                    | DRBG Internal State       |                   |       |          | О       |

|                                                 |                            | DRBG Seed                 |                   |       |          | 0       |

|                                                 |                            | DRBG Entropy Input String |                   |       |          | 0       |

|                                                 |                            | CO Password               |                   |       |          | 0       |

|                                                 |                            | User Password             |                   |       |          | 0       |

|                                                 |                            | MEK                       |                   |       |          | 0       |

| Cryptographic                                   | Get Random<br>Number       | DRBG Internal State       | О                 |       | О        | О       |

| Cryptographic<br>Officer, User and<br>FW Loader |                            | DRBG Seed                 | О                 |       | 0        | О       |

|                                                 |                            | DRBG Entropy Input String | О                 |       | 0        | 0       |

| Cryptographic<br>Officer, User and<br>FW Loader | Get MSID                   | N/A                       |                   | N     | J/A      |         |

| Cryptographic<br>Officer, User and<br>FW Loader | Show Status                | N/A                       |                   | N     | J/A      |         |

| Cryptographic<br>Officer, User and<br>FW Loader | Self-test                  | N/A                       |                   | N     | J/A      |         |

<u>Exhibit 27</u> – *Unauthenticated Service, Cryptographic Keys & CSPs and Type(s) of Access.*

# 7. Physical security policy

The following physical security mechanisms are implemented in a cryptographic module:

- The Module consists of production-grade components enclosed in an aluminum alloy enclosure, which is opaque within the visible spectrum. The top panel of the enclosure can be removed by unscrewing screws. However, the module is sealed with tamper-evident labels in accordance with FIPS 140-2 Level 2 Physical Security requirements so that tampering is easily detected when the top and bottom cases are detached.

- 2 tamper-evident labels are applied over both top and bottom cases of the module at the factory. The tamper-evident labels are not removed and reapplied without tamper evidence.

The following table summarizes the actions required by the Cryptographic Officer Role to ensure

that physical security is maintained:

| Physical Security<br>Mechanisms  | Recommended<br>Frequency of<br>Inspection/Test | Inspection/Test Guidance Details                                                                                                        |

|----------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Production grade cases           | As often as feasible                           | Inspect the entire perimeter for cracks, gouges, lack of screw(s) and other signs of tampering. Remove from service if tampering found. |

| Tamper-evident<br>Sealing Labels |                                                | Inspect the sealing labels for scratches, gouges, cuts and other signs of tampering. Remove from service if tampering found.            |

<u>Exhibit 28</u> - Inspection/Testing of Physical Security Mechanisms (FIPS 140-2 Table C5)

Exhibit 29 – Signs of Tamper

NOTE 3: Samsung Electronics Co., Ltd has excluded the following components as per AS01.09:

| Items     | <b>BOM</b> Code | Applicable to Hardware Version(s) |

|-----------|-----------------|-----------------------------------|

| Resistor  | 2007-007136     | MZILT800HAHQ-000C9                |

|           |                 | MZILT960HAHQ-000C9                |

|           |                 | MZILT960HAHQ-00AC9                |

| Resistor  | 2007-000972     | MZILT800HAHQ-000C9                |

|           |                 | MZILT960HAHQ-000C9                |

|           |                 | MZILT1T6HAJQ-000C9                |

|           |                 | MZILT1T9HAJQ-000C9                |

|           |                 | MZILT3T2HALS-000C9                |

|           |                 | MZILT3T8HALS-000C9                |

|           |                 | MZILT7T6HMLA-000C9                |

|           |                 | MZILT960HAHQ-00AC9                |

|           |                 | MZILT1T9HAJQ-00AC9                |

|           |                 | MZILT3T8HALS-00AC9                |

|           |                 | MZILT7T6HMLA-00AC9                |

| Resistor  | 2007-000033     | MZILT1T6HAJQ-000C9                |

|           |                 | MZILT1T9HAJQ-000C9                |

|           |                 | MZILT3T2HALS-000C9                |

|           |                 | MZILT3T8HALS-000C9                |

|           |                 | MZILT7T6HMLA-000C9                |

|           |                 | MZILT1T9HAJQ-00AC9                |

|           |                 | MZILT3T8HALS-00AC9                |

|           |                 | MZILT7T6HMLA-00AC9                |

| Capacitor | 2203-009818     | MZILT800HAHQ-000C9                |

|           |                 | MZILT960HAHQ-000C9                |

|           |                 | MZILT1T6HAJQ-000C9                |

|           |                 | MZILT1T9HAJQ-000C9                |

|           |                 | MZILT3T2HALS-000C9                |

|           |                 | MZILT3T8HALS-000C9                |

|           |                 | MZILT7T6HMLA-000C9                |

|           |                 | MZILT15THMLA-000C9                |

|           |                 | MZILT30THMLA-000C9                |

|           |                 | MZILT960HAHQ-00AC9                |

|           |                 | MZILT1T9HAJQ-00AC9                |

|           |                 | MZILT3T8HALS-00AC9                |

|           |                 | MZILT7T6HMLA-00AC9                |

|           |                 | MZILT15THMLA-00AC9                |

| Capacitor | 2203-008953     | MZILT800HAHQ-000C9                |

|           |                 | MZILT960HAHQ-000C9                |

|           |                 | MZILT1T6HAJQ-000C9                |

|           |                 | MZILT1T9HAJQ-000C9                |

|           |                 | MZILT3T2HALS-000C9                |

|            |                 | MZILT3T8HALS-000C9 |

|------------|-----------------|--------------------|

|            |                 | MZILT7T6HMLA-000C9 |

|            |                 | MZILT15THMLA-000C9 |

|            |                 | MZILT30THMLA-000C9 |

|            |                 | MZILT960HAHQ-00AC9 |

|            |                 | MZILT1T9HAJQ-00AC9 |

|            |                 | MZILT3T8HALS-00AC9 |

|            |                 | MZILT7T6HMLA-00AC9 |

|            |                 | MZILT15THMLA-00AC9 |

| Capacitor  | 2203-009815     | MZILT15THMLA-000C9 |

|            |                 | MZILT30THMLA-000C9 |

|            |                 | MZILT15THMLA-00AC9 |

| Capacitor  | 2203-000206     | MZILT15THMLA-000C9 |

|            |                 | MZILT30THMLA-000C9 |

|            |                 | MZILT15THMLA-00AC9 |

| Capacitor  | 2203-009805     | MZILT30THMLA-000C9 |

| Storage IC | K9DVGB8JBM-7### | MZILT30THMLA-000C9 |

|            |                 |                    |

# **Exhibit 30** – Excluded components

The above power electronics are used for MLCC power and do not process any CSPs, Plaintext data, or other information that if misused could lead to compromise.

# 8. Electromagnetic Interference/Electromagnetic Compatibility (EMI/EMC)

The cryptographic module conforms to the EMI/EMC requirements specified by 47 Code of Federal Regulations, Part 15, Subpart B, Unintentional Radiators, Digital Devices, Class B.

# 9. Mitigation of Other Attacks Policy

The cryptographic module has not been designed to mitigate any specific attacks beyond the scope of FIPS 140-2.

| Other   | Mitigation | Specific    |

|---------|------------|-------------|

| Attacks | Mechanism  | Limitations |

| N/A     | N/A        | N/A         |

Exhibit 31 - Mitigation of Other Attacks (FIPS 140-2 Table C6)

# 10. Security rules

The following specifies the security rules under which the cryptographic module shall operate in accordance with FIPS 140-2:

- The cryptographic module operates always in FIPS Mode once shipped from the vendor's manufacturing site.

- The steps necessary for the secure installation, initialization and start-up of the cryptographic module as per FIPS 140-2 VE10.03.01 are as follows:

#### 10.1. Secure Installation

- o Step1. User should examine the tamper evidence

- Inspect the entire perimeter for cracks, gouges, lack of screw(s) and other signs of tampering including the tamper evident sealing label.

- If there is any sign of tampering, do not use the product and contact Samsung.

- o Step2. Identify the firmware version in the device

- Confirm that the firmware version is equivalent to the version(s) listed in this document via SCSI Inquiry command.

- o Step3. Take the drive's ownership

- Change SID's PIN by setting a new PIN

- Change EraseMaster's PIN by setting a new PIN

- Erase Method on each LBA Range to rekey the encryption key

- Change BandMaster0~7's PIN by setting new PINs

- Configure the LBA Range(s) by setting ReadLockEnabled and WriteLockEnabled columns to True

- Don't change LockOnReset column in Locking Table so that the drive always gets locked after a power cycle

- o Step4. Configure FW download and Diagnostic features

- Disable Makers Class using SID Authority to disable FW download and Diagnostic features

- Enable Makers Class only when FW download and Diagnostic features are needed

- o Step5. Periodically examine the tamper evidence

- If there is any sign of tampering, stop using the product to avoid a potential security hazard or information leakage.

## 10.2. Operational description of Module

- The cryptographic module shall maintain logical separation of data input, data output, control input, status output, and power.

- The cryptographic module shall not output CSPs in any form.

- The cryptographic module shall use the Approved DRBG for generating all cryptographic keys.

- The cryptographic module shall enforce role-based authentication for security relevant services.

- The cryptographic module shall enforce a limited operational environment by the secure firmware load test using RSA PSS-2048 with SHA-256.

- The cryptographic module shall provide a production-grade, opaque, and tamper-evident cryptographic boundary.

- The cryptographic module enters the error state upon failure of Self-tests. All commands from the Host (General Purpose Computer (GPC) outside the cryptographic boundary) are rejected in the error state and the cryptographic module returns a sense key (0x4) via the status output. Cryptographic services and data output are explicitly inhibited when in the error state.

- The cryptographic module satisfies the requirements of FIPS 140-2 IG A.9 (i.e. key\_1 ≠ key\_2)

- The module generates at a minimum 256 bits of entropy for use in key generation.

#### 10.3. Power-on Self-Tests

| Algorithm         | Test                                                                                   |  |  |

|-------------------|----------------------------------------------------------------------------------------|--|--|

| AES               | Encrypt KAT and Decrypt KAT for AES-256-XTS at power-on                                |  |  |

| SHS (Cert. #4178) | KAT for SHA-256 at power-on                                                            |  |  |

| SHS (Cert. #4179) | KAT for SHA-256 at power-on                                                            |  |  |

| DRBG              | KAT for Hash_DRBG (SHA-256) at power-on                                                |  |  |

| RSA               | Firmware integrity check using RSA PSS-2048 SHA-256 signature verification at power-on |  |  |

### Exhibit 32 – Power-on Self-tests.

- Conditional Self-test

- o Pairwise consistency: N/A

- o Bypass Test: N/A

- o Manual key entry test: N/A

- o F/W load test

- F/W load test is performed by using RSA algorithm with PSS-2048 and SHA-256

- o Continuous random number generator test on Approved DRBG

- o Continuous random number generator test on NDRNG