Common Criteria for Information Technology Security Evaluation

# V-WAY64 V3.0 (µPD79216000) Security Target Lite

| Approved By   |  | Checked By | V. | Prepared By |  |  |

|---------------|--|------------|----|-------------|--|--|

| J.F. CHOUTEAU |  | J.F. LEON  |    | J.F. LEON   |  |  |

# Revisions

| Revision date | Version | Author    | Comments                  |

|---------------|---------|-----------|---------------------------|

| 2004-July-12  | 1.00    | J.F. LEON | Final review and Release. |

# Table of contents

| Chapter 1 ST Lite introduction                                            | 6  |

|---------------------------------------------------------------------------|----|

| 1.1 ST Lite identification                                                | 6  |

| 1.2 ST Lite overview                                                      |    |

| 1.3 CC conformance claim                                                  | 7  |

| Chapter 2 TOE description                                                 | 8  |

| 2.1 Product type                                                          |    |

| 2.2 Smartcard product life cycle                                          |    |

| 2.3 TOE environment.                                                      |    |

| 2.3.1 Development environment of the TOE                                  |    |

| 2.3.2 Production environment of the TOE                                   |    |

| 2.3.3 User environment of the TOE                                         | 14 |

| 2.4 TOE logical phases                                                    | 14 |

| 2.5 TOE intended usage                                                    | 14 |

| 2.6 General IT features of the TOE                                        | 14 |

| Chapter 3 TOE security environment                                        | 15 |

| 3.1 Assets                                                                |    |

| 3.2 Assumptions                                                           |    |

| 3.2.1 Assumptions on phase 1                                              |    |

| 3.2.2 Assumptions on the TOE delivery process (phases 4 to 7)             |    |

| 3.2.3 Assumptions on phases 4 to 6                                        |    |

| 3.2.4 Assumptions on phase 7                                              | 16 |

| 3.3 Threats                                                               |    |

| 3.3.1 Unauthorised full or partial cloning of the TOE                     |    |

| 3.3.2 Threats on phase 1 (delivery and verification procedures)           | 17 |

| 3.3.3 Threats on phases 2 to 7                                            |    |

| 3.4 Organisational security policies                                      | 19 |

| Chapter 4 Security objectives                                             | 20 |

| 4.1 Security objectives for the TOE                                       |    |

| 4.2 Security objectives for the environment                               | 21 |

| 4.2.1 Objectives on phase 1                                               | 21 |

| 4.2.2 Objectives on phase 2 (development phase)                           |    |

| 4.2.3 Objectives on phase 3 (manufacturing phase)                         |    |

| 4.2.4 Objectives on the TOE delivery process (phase 4 to 7)               |    |

| 4.2.5 Objectives on phases 4 to 6                                         |    |

| 4.2.6 Objectives on phase 7                                               |    |

| Chapter 5 IT security requirements                                        | 24 |

| 5.1 TOE security functional requirements                                  | 24 |

| 5.1.1 Functional Requirements applicable to phase 3 only (testing phase). | 24 |

| 5.1.2 Functional requirements applicable to phases 3 to 7                 |    |

| 5.2 TOE security assurance requirements                                   |    |

| 5.2.1 ADV_IMP.2 Implementation of the TSF                                 |    |

| 5.2.2 ALC_DVS.2 Sufficiency of security measures                          |    |

| 5.2.3 AVA_VLA.4 Highly resistant                                          |    |

| 5.3 Security requirements for the IT environment                          |    |

| Chapter 6 TOE summary specification                                       |    |

| 6.1     | TOE security functions                                                     |    |

|---------|----------------------------------------------------------------------------|----|

| 6.1.    |                                                                            |    |

| 6.1.    |                                                                            |    |

| 6.1.    |                                                                            |    |

| 6.1.    | • • •                                                                      |    |

| 6.1.    |                                                                            |    |

| 6.1.    |                                                                            |    |

| 6.1.    |                                                                            |    |

| 6.1.    |                                                                            |    |

| 6.1.    |                                                                            |    |

| 6.1.    | 10 DES cryptography (SF10)                                                 |    |

| 6.1.    | 11 Mapping between security functions and security functional requirements |    |

| 6.2     | Assurance measures                                                         |    |

| 6.2.    | 1 Security target (AM1)                                                    | 39 |

| 6.2.    | 2 CM documentation (AM2)                                                   | 39 |

| 6.2.    |                                                                            |    |

| 6.2.    |                                                                            |    |

| 6.2.    | 5 Functional specification (AM5)                                           | 40 |

| 6.2.    |                                                                            |    |

| 6.2.    |                                                                            |    |

| 6.2.    | ε                                                                          |    |

| 6.2.    |                                                                            |    |

|         | 10 TOE security policy model (AM10)                                        |    |

|         | 11 Development security (AM11)                                             |    |

|         | 12 Life cycle definition (AM12)                                            |    |

|         | 13 Test documentation (AM13)                                               |    |

|         | 14 TOE for testing (AM14)                                                  |    |

|         | 15 Documentation analysis (AM15)                                           |    |

|         | 16 Strength of TOE security functions (AM16)                               |    |

|         | 17 Vulnerability analysis (AM17)                                           |    |

| 6.2.    | 18 Trace of assurance measures to assurance requirements                   | 41 |

| Chapte  | r 7 PP claims                                                              | 42 |

| 7.1     | PP reference                                                               |    |

| 7.2     | PP tailoring                                                               |    |

| 7.3     | PP additions                                                               |    |

| Annex A |                                                                            |    |

| A.1     | Abbreviations and acronyms                                                 |    |

| A.2     | Vocabulary                                                                 |    |

| A.3     | References                                                                 |    |

| 11.5    |                                                                            |    |

# List of tables

| Table 3.1 - Class Statement of Threats versus Phases                                              | 19 |

|---------------------------------------------------------------------------------------------------|----|

| Table 5.1 - Branch access control matrix                                                          | 27 |

| Table 5.2 - Data access control matrix                                                            | 27 |

| Table 5.3 - List of subjects, information and operations for testing information flow control SFP | 28 |

| Table 5.4 - TEST_ROM information flow control                                                     | 28 |

| Table 5.5 - OTP2 information flow control.                                                        | 29 |

| Table 5.6 - TEST_SFR information flow control                                                     | 29 |

| Table 5.7 - Auditable events indicating a potential security violation                            | 30 |

| Table 5.8 - Resistance to physical attack.                                                        | 31 |

| Table 6.1 - Relationship between security requirements and security functions                     | 39 |

| Table 6.2 - Relationship between assurance requirements and assurance measures                    | 41 |

# List of figures

| Figure 2.1 - Microcontroller block diagram | . 10 | 0 |

|--------------------------------------------|------|---|

| Figure 2.2 - Smartcard product life cycle  | . 12 | 2 |

# Chapter 1 ST Lite introduction

## **1.1 ST Lite identification**

- 1 <u>ST Lite title</u>: V-WAY64 V3.0 (µPD79216000) Security Target Lite

- 2 <u>ST Lite version number</u> : V1.00-Ref:33-55N1-10001

#### TOE identity

#### 3 The TOE, identified V-WAY64 V3.0, is composed of:

- µPD79216000 (V-WAY64) microcontroller from NEC, Version 3.0 (labelled V01005V30054)

- and the libraries delivered in linkable-form:

- LLL (Low-Level Library) Version 3.0: LibcryptLLL.a

- RSA (PKCS 1.5) Version 2.0: RSAlib.a

- 4 This ST Lite has been built with the CC version 2.1.

- 5 Annex A gives a glossary of terms used in this ST Lite, as well as of the referenced documents.

## **1.2** ST Lite overview

- 6 This ST Lite is produced in the frame of the security evaluation and certification of  $\mu$ PD79216000 V3.0, known hereafter in the ST Lite as V-WAY64 V3.0. This security evaluation and certification is conducted under the French IT Security Evaluation and Certification Scheme, with the work of DCSSI, as the Certification Body, and of CEACI as the Evaluation Laboratory (also called ITSEF).

- 7 The intent of this ST Lite is to specify the functional and assurance requirements that are applicable to the V-WAY64 V3.0 microcontroller used as a smartcard integrated circuit for smartcard applications.

- 8 A smartcard is usually seen as a credit card sized card having a non-volatile memory and a processing unit embedded within it.

- 9 The complex development and manufacturing processes of a smartcard before it is issued to the users can be separated into three distinct stages:

- <u>The development stage</u>: Microcontroller design, smartcard embedded software development, application software development, integration and photomask fabrication.

- <u>The production stage</u>: Microcontroller manufacturing, testing, preparation and shipping to the module and card assembly line.

- The smartcard production stage: Microcontroller packaging into a module (with testing), first, then into the plastic card body, and finally the smartcard product finishing process with printing and testing. After these operations, the smartcard is prepared and shipped to the personalisation line.

#### In addition, two other important stages are considered into the smartcard life cycle:

- The smartcard personalisation and testing stage where the end-user data are loaded into the smartcard's memory.

- The smartcard usage by its issuers and end-user.

- 11 The increase in the number and complexity of applications in the smartcard market is reflected in the increase of the level of data security required. The security needs for a smartcard can be summarised as being able to counter those who want to defraud, gain unauthorised access to data and control a system using a smartcard.

10

12 Therefore it is mandatory to:

- Maintain the integrity and the confidentiality of the content of the smartcard non-volatile memory (program and data memories).

- Maintain the integrity and the confidentiality of the security enforcing and security relevant architectural components (security mechanisms and associated functions) embedded into the integrated circuit.

- 13 Protected information is in general secret data as Personal Identification Numbers, Balance Value (Stored Value Cards), and Personal Data Files. Another set of protected information is the access rights; these include any cryptographic algorithms and keys needed for accessing and using the services provided by the system through use of the smartcard.

- 14 The intended environment is very large; and generally once issued the smartcard can be stored and used anywhere in the world, at any time, and no control can be applied to the smartcard and the end-user. An exception to this is the controls that are applicable when the smartcard is in its end usage in the system working according to its specifications.

- 15 Presently the major smartcard applications, where the V-WAY64 V3.0 microcontroller from NEC may be used, are:

- Banking and finance market for credit/debit cards, electronic purse (stored value cards) and electronic commerce.

- Network based transaction processing such as mobile phones (GSM SIM cards), pay-TV (subscriber and pay-per-view cards), communication highways (Internet access and transaction processing).

- Transport and ticketing market (access control cards).

- ☞ Governmental cards (ID-cards, health cards, driver license etc.).

- New emerging sectors such as the multimedia commerce and Intellectual Proprietary Rights protection.

- 16 The main objectives of this ST Lite are to:

- Describe the Target of Evaluation (TOE) as a product and position it in the life cycle of the smartcard. The ST Lite includes the development and the production phase of the microcontroller with its dedicated software, without the smartcard embedded software development phase.

- Describe the security environment of the TOE including the assets to be protected and the threats to be countered by the TOE and by the operational environment during the development, production phases.

- Describe the security objectives for the TOE and for its environment in terms of integrity and confidentiality of application data and programs, protection of the TOE and associated documentation during the development and production phases.

- Specify the security requirements that include the TOE security functional requirements and the TOE security assurance requirements.

- ☞ Describe the TSF.

## **1.3** CC conformance claim

- 17 This ST Lite has been built with Common Criteria for Information Technology Security Evaluation, Version 2.1 (cf. Ref. [1], [2], [3]), as the following:

- ☞ Part 2 conformant,

- ☞ Part 3 conformant with EAL4 augmented level,

- ☞ PP/9806 (cf. Ref. [6]) conformant.

- 18 The EAL4 level from CC Part 3 is augmented with the assurance components ADV\_IMP.2, ALC\_DVS.2 and AVA\_VLA.4.

# **Chapter 2 TOE description**

19 This part of the ST Lite describes the TOE as an aid to the understanding of its security requirements and address the product type, the intended usage and the general IT features of the TOE.

## 2.1 **Product type**

- 20 The TOE is composed of the single chip microcontroller unit named V-WAY64 V3.0, independent of the physical interface and the way it is packaged, and the libraries LLL V3.0 and RSA V2.0.

- 21 The V-WAY64 V3.0 is a security cryptocontroller, to be used in a smartcard product.

22 The TOE runs according to two main modes:

- <u>Test mode</u>: it is a special mode which must only run at the end of the production phase to test that the TOE works properly. Then, the device is definitely locked in user mode.

- ☞ <u>User mode</u>: this is the normal operating mode.

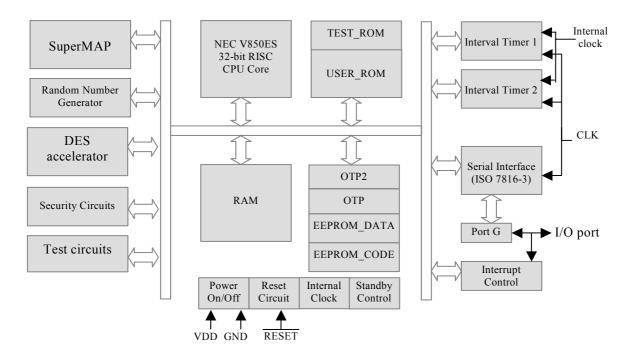

- 23 The TOE has got the following dedicated features:

#### **Processing unit**

A NEC V850ES CPU core, which is a small-size 32-bit RISC engine based on the Harvard architecture, with 32 "general purpose" registers of 32 bits and a processing mode using a 5-stage pipeline with short-path and automatic wait insertion. Dedicated to embedded applications, the core has 83 specific instructions with: bit, byte, half-word and word manipulation. The instruction set is well suited for greater code compactness and low power consumption.

#### **Memories**

- ☞ 192 Kbytes of ROM, named USER ROM, split in:

- a "system" domain named SOS,

- an "application" domain named AOS.

- 8 Kbytes of a ROM area (named TEST\_ROM) dedicated to the IC test firmware. The TEST\_ROM area is only accessible in test mode, but not in user mode.

- ☞ 64 Kbytes of EEPROM split in:

- a "code and data" domain named EEPROM CODE,

- a "data only" domain named EEPROM DATA,

- a 64-byte OTP page, named OTP, divided in read-only 32-byte "NEC OTP" area including a unique identification number, and 32-byte "User OTP" area.

- 64 bytes of OTP, named OTP2, dedicated to the TSF data. OTP2 is only accessible in test mode, but not in user mode.

- ☞ SFR area, split in:

- USER\_SFR, which contains the user-accessible registers,

- TEST\_SFR, which contains registers only visible for testing.

- ☞ 4 Kbytes of RAM.

- 24 <u>Note</u>: The high voltage required for writing or erasing operations in EEPROM, and writing operations in OTP and OTP2 is produced internally.

#### Crypto-processor

- The V-WAY64 V3.0 microcontroller is equipped with a NEC SuperMAP coprocessor for fast public key encryption. The NEC SuperMAP enables high-speed arithmetic and modular operations, such as multiplication and exponentiation on large numbers up to 2048 bits long. The SuperMAP access for software developers must be made through a set of arithmetic and modular routines delivered in a linkable-form library, known as Low-Level Library (LLL).

- A secure 1024-bit RSA library, which is making use of some of the LLL, and the LLL itself are part of the TOE.

#### **DES** accelerator

The DES accelerator is a dedicated hardware intended to perform fast DES encryption and decryption. The DES accelerator provides support to triple-DES ECB and CBC operations.

#### **Clock generator**

☞ Internal clock, up to 36 MHz.

#### random number generator

☞ 1 16-bit random number generator.

#### Timers

☞ 2 16-bit timers, with either internal or external clock source.

#### Interrupt controller

- ☞ 7 maskable internal interrupts.

- ☞ 2 exception traps.

- ☞ 32 software exceptions.

- ☞ 8 levels of interrupt priority

#### I/O port

☞ 1 I/O port with smart serial interface conforming to ISO 7816-3 and EMV standards (cf. Ref. [4], [5]), for smartcard communication protocol.

#### Security circuits

- The V-WAY64 V3.0 is equipped with a full set of security circuits that:

- shield the device from unspecified voltage and frequency range, exposure to UV light and physical attacks, illegal operations on memory areas

- make more difficult from outside, the analysis of internal activity of the device.

#### **Standby functions**

☞ HALT, IDLE, STOP.

#### Power On/Off circuit

- ☞ Reset generator,

- Internal voltage regulator.

#### **Test circuits**

- The TOE includes test circuits. After completion of the testing operations, the device is definitively locked in user mode.

- ☞ To perform the tests, an IC dedicated software is included in the TOE. In accordance with the definition in the PP/9806 (cf. Ref. [6]), this IC dedicated software is composed with both an IC test firmware, masked within the TEST\_ROM, and tests programs outside the IC.

Figure 2.1 - Microcontroller block diagram

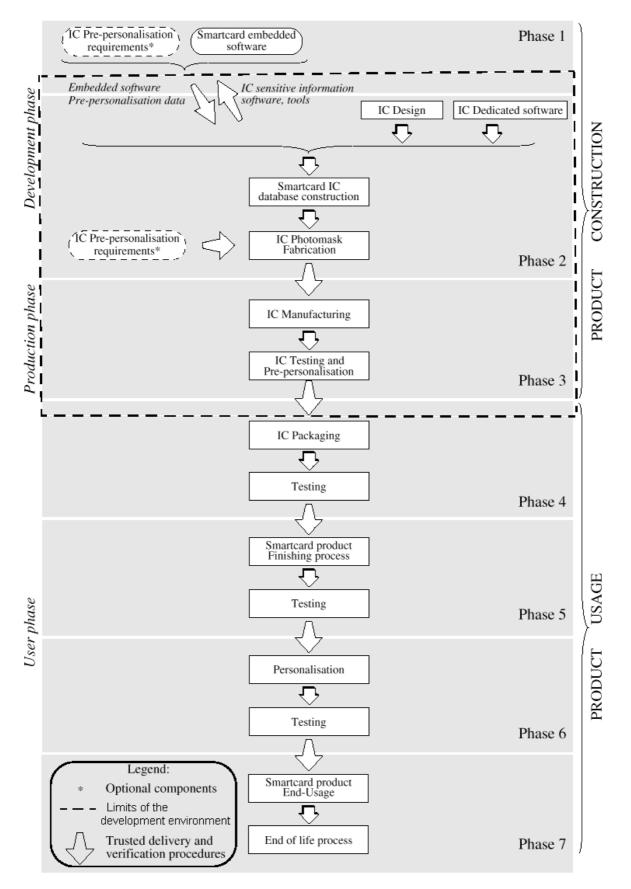

## 2.2 Smartcard product life cycle

25 The smartcard product life cycle is decomposed into 7 phases where the following authorities are involved:

| Phase 1 | Smartcard         | The smartcard embedded software developer is in          |

|---------|-------------------|----------------------------------------------------------|

|         | embedded software | charge of the smartcard embedded software                |

|         | development       | development and the specification of IC pre-             |

|         |                   | personalisation requirements.                            |

| Phase 2 | IC development    | The IC designer designs the IC, develops IC              |

|         |                   | dedicated software, provides information, software or    |

|         |                   | tools to the smartcard embedded software developer,      |

|         |                   | and receives the smartcard embedded software from        |

|         |                   | the developer, through trusted delivery and              |

|         |                   | verification procedures. From the IC design, IC          |

|         |                   | dedicated software and smartcard embedded                |

|         |                   | software, he constructs the smartcard IC database,       |

|         |                   | necessary for the IC photomask fabrication.              |

| Phase 3 | IC manufacturing  | The IC manufacturer is responsible for producing         |

|         | and testing       | the IC through three main steps: IC manufacturing,       |

|         |                   | IC testing, and IC pre-personalisation.                  |

| Phase 4 | IC packaging and  | The IC packaging manufacturer is responsible for         |

|         | testing           | the IC packaging and testing.                            |

| Phase 5 | Smartcard product | The smartcard product manufacturer is                    |

|         | finishing process | responsible for the smartcard product finishing          |

|         |                   | process and testing.                                     |

| Phase 6 | Smartcard         | The <b>personaliser</b> is responsible for the smartcard |

|         | personalisation   | personalisation and final tests. Other smartcard         |

|         |                   | embedded software may be loaded onto the chip at         |

|         |                   | the personalisation process.                             |

| Phase 7 | Smartcard         | The smartcard issuer is responsible for the              |

|         | end-usage         | smartcard product delivery to the smartcard              |

|         |                   | end-user, and the end of life process.                   |

- 26 The limits of this ST Lite correspond to the phases 2 and 3, including the phase 1 delivery and verification procedures and the TOE delivery to the IC packaging manufacturer. Procedures corresponding to phases 1, 4, 5, 6 and 7 are outside the scope of this ST Lite.

- 27 The figure that following describes the smartcard product life cycle.

Figure 2.2 - Smartcard product life cycle

## **2.3 TOE environment**

28

- Considering the TOE, three types of environments were identified:

- Development environment corresponding to phase 2,

- Production environment corresponding to phase 3,

- ☞ User environment, from phase 4 to phase 7.

## **2.3.1** Development environment of the TOE

- 29 To assure security, the environment in which the development takes place shall be made secured with controllable accesses having traceability. Furthermore, it is important that all authorised personnel involved fully understand the importance and the rigid implementation of defined security procedures.

- 30 The development begins with the TOE's specification. All parties in contact with sensitive information are required to abide by Non-Disclosure Agreement's.

- 31 Design and development of the IC then follows. The engineer uses a secure computer system (preventing unauthorised access) to make his design simulations, circuit performance verifications and generation of the TOE's IC photomask databases. Sensitive documents, databases on tapes, diskettes, and printed circuit layout information are stored in appropriate locked cupboards/safe. Of paramount importance also is the disposal of unwanted data (complete electronic erasures) and documents (e.g. shredding).

- 32 Reticles and photomasks are generated from the verified IC databases; the formers are used in the silicon Wafer-fab processing. When reticles and photomasks are generated off-site, they are transported and worked on in a secure environment with accountability and traceability of all (good and bad) products. During the transfer of sensitive data electronically, procedures shall be established to ensure that the data arrive only at the destination and are not accessible at intermediate stages (e.g. stored on a buffer server where system administrators make backup copies).

## **2.3.2 Production environment of the TOE**

- 33 As high volumes of product commonly go through such environment, adequate control procedures are necessary to account for all pieces at all stages of production.

- 34 Production starts within the Wafer-fab; here the silicon wafers undergo the diffusion processing. Computer tracking at wafer level throughout the process is commonplace. The wafers are then taken into the test area. Testing and security programming (optional) of each TOE occurs. After fabrication, the TOE is tested to assure conformance with the device specification. The wafers will then be securely delivered for assembly onto the smartcard.

- 35 Whether carried out under the control of the IC manufacturer or the packaging manufacturer, wafers shall be scribed and broken such as to separate the functional from the non-functional ICs. The latter is discarded in a controlled accountable manner. The good ICs are then packaged. When testing, programming and deliveries are done offsite, ICs shall be transported and worked on in a secure environment with accountability and traceability of all (good and bad) products. Further testing occurs, followed by smartcard personalisation, retesting then delivery to the smartcard issuer.

## **2.3.3** User environment of the TOE

- 36 The TOE user environment is the environment of phases 4 to 7.

- 37 At phases 4, 5 and 6, the TOE user environment is a controlled environment.

- 38 Phase 7 is the end-user environment that covers a wide spectrum of very different functions, thus making it difficult to avoid and monitor any abuse of the TOE.

- 39 The TOE user environment is not covered by the present ST Lite.

## **2.4 TOE logical phases**

- 40 During its construction usage, the TOE may be under several life logical phases.

- 41 These phases are sorted under a logical controlled sequence. The change from one phase to the next shall be under the TOE control.

## **2.5 TOE** intended usage

- 42 The TOE can be incorporated in several applications such as those described inside the paragraph 15.

- 43 During the phases 1, 2 and 3, the TOE is being developed and produced. The **administrators** are the following:

- The smartcard embedded software developer,

- ☞ The IC designer,

- ☞ The IC manufacturer.

## **2.6** General IT features of the TOE

44

The TOE IT functionalities consist of data storage and processing such as:

- Arithmetical functions (e.g. incrementing counters in electronic purses, calculating currency conversion in electronic purses...);

- Data communication;

- Cryptographic operations (e.g. data encryption/decryption, digital signature verification), when applicable.

## Chapter 3 TOE security environment

45 This section describes the security aspects of the environment in which the TOE is intended to be used and addresses the description of the assumptions, the assets to be protected, the threats and the organisational security policies.

## 3.1 Assets

46

Assets are security relevant elements of the TOE that include:

- The application data of the TOE (such as IC pre-personalisation requirements, IC and system specific data),

- The smartcard embedded software,

- ☞ The IC dedicated software,

- ☞ The IC specification, design, development tools and technology.

- 47 The TOE itself is therefore an asset.

- 48 Assets have to be protected in terms of confidentiality and integrity.

## **3.2 Assumptions**

49 It is assumed that this section concerns the following items:

- Due to the definition of the TOE limits, any assumption for the smartcard embedded software development (phase 1 is outside the scope of the TOE).

- Any assumption from phases 4 to 7 for the secure usage of the TOE, including the TOE delivery procedures.

50 Security is always the matter of the whole system: the weakest element of the chain determines the total system security. Assumptions described hereafter have to be considered for a secure system using smartcard products:

- Assumptions on phase 1,

- ☞ Assumptions on the TOE delivery process (phases 4 to 7),

- Assumptions on phases 4-5-6,

- Assumptions on phase 7.

## **3.2.1** Assumptions on phase 1

- A.SOFT\_ARCHI The smartcard embedded software shall be developed in a secure manner, that is focusing on the integrity of program and of data.

- A.DEV\_ORG Procedures dealing with physical, personnel, organisational, technical measures for the confidentiality and integrity of smartcard embedded software (e.g. source code and any associated documents) and IC designer proprietary information (tools, software, documentation...) shall exist and be applied in software development.

## **3.2.2** Assumptions on the TOE delivery process (phases 4 to 7)

- 51 Procedures shall guarantee the control of the TOE delivery and storage process and the conformance to its objectives as described in the following assumptions.

- A.DLV\_PROTECT Procedures shall ensure protection of TOE material/information under delivery and storage.

- A.DLV\_AUDIT Procedures shall ensure that corrective actions are taken in case of improper operation in the delivery process and storage.

A.DLV\_RESP Procedures shall ensure that people dealing with the procedure for delivery, has got the required skill.

## **3.2.3** Assumptions on phases 4 to 6

- A.USE\_TEST It is assumed that appropriate functionality testing of the IC is used in phases 4, 5 and 6.

- A.USE\_PROD It is assumed that security procedures are used during all manufacturing and test operations through phases 4, 5, 6 to maintain confidentiality and integrity of the TOE and of its manufacturing and test data (to prevent any possible copy, modification, retention, theft or unauthorised use).

## **3.2.4** Assumptions on phase 7

- A.USE\_DIAG It is assumed that secure communication protocols and procedures are used between smartcard and terminal.

- A.USE\_SYS It is assumed that the integrity and the confidentiality of sensitive data stored/handled by the system (terminals, communications...) is maintained.

## 3.3 Threats

- 52 The TOE as defined in Chapter 2 is required to counter the threats described hereafter; a threat agent wishes to abuse the assets either by functional attacks, environmental manipulations, specific hardware manipulations or by any other types of attacks.

- 53 Threats have to be split in:

- Threats against which specific protection within the TOE is required (class I),

- Threats against which specific protection within the environment is required (class II).

## **3.3.1** Unauthorised full or partial cloning of the TOE

T.CLON Functional cloning of the TOE (full or partial) appears to be relevant to any phases of the TOE life cycle, from phase 1 to phase 7.

Generally, this threat is derived from specific threats combining unauthorised disclosure, modification or theft of assets at different phases. Specially, some functionalities of the TOE may be cloned by observing its behaviour or getting information by reverse engineering.

## **3.3.2** Threats on phase 1 (delivery and verification procedures)

- 54 Considering the limits of the TOE, two types of threats have to be considered during phase 1:

- Threats on the assets transmitted from the IC designer to the embedded software developer during the smartcard development.

- Threats on the smartcard embedded software and any additional application data transmitted during the delivery process from the embedded software developer to the IC designer.

- 55 These threats are described hereafter:

- T.DIS\_INFO Unauthorised disclosure of the assets delivered by the IC designer to the smartcard embedded software developer such as sensitive information on IC specification, design and technology, software and tools if applicable.

- T.DIS\_DEL Unauthorised disclosure of the smartcard embedded software and any additional application data (such as IC prepersonalisation requirements) during the delivery process to the IC designer.

- T.MOD\_DEL Unauthorised modification of the smartcard embedded software and any additional application data (such as IC prepersonalisation requirements) during the delivery process to the IC designer.

- T.T\_DEL Theft of the smartcard embedded software and any additional application data (such as IC pre-personalisation requirements) during the delivery process to the IC designer.

## **3.3.3** Threats on phases 2 to 7

- During these phases, the assumed threats could be described in three types:

- Unauthorised disclosure of assets,

- Theft or unauthorised use of assets,

- Unauthorised modification of assets.

#### Unauthorised disclosure of assets

- 57 This type of threats covers unauthorised disclosure of assets by attackers who may possess a wide range of technical skills, resources and motivation. Such attackers may also have technical awareness of the product.

- T.DIS DESIGN Unauthorised disclosure of IC design.

- This threat covers the unauthorised disclosure of proprietary elements such as IC specification, IC design, IC technology detailed information, IC hardware security mechanism specifications.

- T.DIS\_SOFT Unauthorised disclosure of smartcard embedded software and data such as access control, authentication system, data protection system, memory partitioning, cryptographic programs.

- T.DIS\_DSOFT Unauthorised disclosure of IC dedicated software.

This threat covers the unauthorised disclosure of IC dedicated software including security mechanisms specifications and implementation.

- T.DIS\_TEST Unauthorised disclosure of test information such as full results of IC testing including interpretations.

- T.DIS\_TOOLS Unauthorised disclosure of development tools.

This threat covers potential disclosure of IC development tools and testing tools (analysis tools, microprobing tools).

T.DIS\_PHMASK Unauthorised disclosure of photomask information, used for photoengraving during the silicon fabrication process.

#### Theft or unauthorised use of assets

Potential attackers may gain access to the TOE and perform operations for which they are not authorised. For example, such attackers may personalise the TOE in an unauthorised manner, or try to gain fraudulous access to the smartcard system.

- T.T\_SAMPLE Theft or unauthorised use of TOE silicon samples (e.g. bond out chips, ...).

- T.T\_PHMASK Theft or unauthorised use of TOE photomasks.

- T.T\_PRODUCT Theft or unauthorised use of smartcard products.

56

#### Unauthorised modification of assets

59 The TOE may be subjected to different types of logical or physical attacks that may compromise security. Due to the intended usage of the TOE (the TOE environment may be hostile), the TOE security parts may be bypassed or compromised reducing the integrity of the TOE security mechanisms and disabling their ability to manage the TOE security. This type of threats includes the implementation of malicious trojan horses.

| T.MOD_DESIGN | Unauthorised modification of IC design.                                                                                                                 |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|              | This threat covers the unauthorised modification of IC specification, IC design including IC hardware security mechanism specifications and realisation |  |  |  |  |

| T.MOD_PHMASK | Unauthorised modification of TOE photomasks.                                                                                                            |  |  |  |  |

| T.MOD_DSOFT  | Unauthorised modification of IC dedicated software including modification of security mechanisms.                                                       |  |  |  |  |

| T.MOD_SOFT   | Unauthorised modification of smartcard embedded software and data.                                                                                      |  |  |  |  |

60

The table below indicates the relationships between the smartcard phases and the threats.

| Threats            | Phase 1  | Phase 2      | Phase 3       | Phase 4   | Phase 5 | Phase 6 | Phase 7 |

|--------------------|----------|--------------|---------------|-----------|---------|---------|---------|

| Functional cloning |          |              |               |           |         |         |         |

| T.CLON             | Class II | Class II     | Class I/II    | Class I   | Class I | Class I | Class I |

|                    | Ur       | nauthorised  | disclosure of | of assets |         |         |         |

| T.DIS_INFO         | Class II |              |               |           |         |         |         |

| T.DIS_DEL          | Class II |              |               |           |         |         |         |

| T.DIS_SOFT         |          | Class II     | Class I/II    | Class I   | Class I | Class I | Class I |

| T.DIS_DSOFT        |          | Class II     | Class I/II    | Class I   | Class I | Class I | Class I |

| T.DIS_DESIGN       |          | Class II     | Class I/II    | Class I   | Class I | Class I | Class I |

| T.DIS_TOOLS        |          | Class II     | Class II      |           |         |         |         |

| T.DIS_PHMASK       |          | Class II     | Class II      |           |         |         |         |

| T.DIS_TEST         |          |              | Class I/II    | Class I   | Class I | Class I |         |

|                    | The      | eft or unaut | horised use   | of assets |         |         |         |

| T.T_DEL            | Class II |              |               |           |         |         |         |

| T.T_SAMPLE         |          | Class II     | Class I/II    | Class I   | Class I |         |         |

| T.T_PHMASK         |          | Class II     | Class II      |           |         |         |         |

| T.T_PRODUCT        |          |              | Class I/II    | Class I   | Class I | Class I | Class I |

|                    | Un       | authorised   | modificatio   | n threats |         |         |         |

| T.MOD_DEL          | Class II |              |               |           |         |         |         |

| T.MOD_SOFT         |          | Class II     | Class I/II    | Class I   | Class I | Class I | Class I |

| T.MOD_DSOFT        |          | Class II     | Class I/II    | Class I   | Class I | Class I | Class I |

| T.MOD_DESIGN       |          | Class II     | Class I/II    | Class I   | Class I | Class I | Class I |

| T.MOD_PHMASK       |          | Class II     | Class II      |           |         |         |         |

#### 3.4 **Organisational security policies**

**P** CRYPTO

The TOE shall offer cryptographic capabilities to embedded software in order to maintain integrity and confidentiality of sensitive data, particularly during transfer outside the TSC.

# Chapter 4 Security objectives

61

- The security objectives of the TOE cover principally the following aspects:

- Integrity and confidentiality of assets.

- Protection of the TOE and associated documentation during development and production phases.

## 4.1 Security objectives for the TOE

- 62 The TOE shall use state of art technology to achieve the following IT security objectives:

- O.TAMPER The TOE must prevent physical tampering with its security critical parts.

Typically, the TOE must include a protection against microprobing. It must also include a protection against security information leakage which could be deduced from the observation of the TOE (such as its power consumption).

O.CLON The TOE functionality needs to be protected from cloning.

For instance, the TOE must prevent the possibility of getting security relevant information by reverse engineering or by observing its behaviour.

O.OPERATE The TOE must ensure the continued correct operation of its security functions.

Particularly, the TOE security functions must be continuously operational so that theft or unauthorised use of silicon samples or smartcard products, or unauthorised modification of its security functions, do not allow to jeopardise the integrity of the TOE.

- O.FLAW The TOE must not contain flaws in design, implementation or operation.

- O.DIS\_MECHAN The TOE shall ensure that the hardware security mechanisms are protected against unauthorised disclosure (such as reverse engineering).

- O.DIS\_MEMORY The TOE shall ensure that sensitive information stored in memories is protected against unauthorised disclosure.

For instance, the TOE must provide a protection against unauthorised access to memory, whether by a logical interface or by a physical attack, in the aim of dumping its contents.

- O.MOD\_MEMORY The TOE shall ensure that sensitive information stored in memories is protected against any corruption or unauthorised modification, by any means (whether by a logical interface or by a physical attack).

- O.CRYPTO The TOE shall provide RSA and DES cryptographic algorithms to perform data encryption/decryption in order to allow smartcard applications to transfer sensitive data out of the TSC in a secure way.

## 4.2 Security objectives for the environment

## 4.2.1 **Objectives on phase 1**

O.DEV\_DIS The IC designer must have procedures to control the sales, distribution, storage and usage of the software and hardware development tools and classified documentation, suitable to maintain the integrity and the confidentiality of the assets of the TOE.

It must be ensured that tools are only delivered to the parties authorised personnel.

It must be ensured that confidential information such as data sheets and general information on defined assets are only delivered to the parties authorised personnel on the need to know basis.

- O.SOFT\_DLV The smartcard embedded software must be delivered from the smartcard embedded software developer (Phase 1) to the IC designer through a trusted delivery and verification procedure that shall be able to maintain the integrity of the software and its confidentiality, if applicable.

- O.SOFT\_MECH To achieve the level of security required by this ST lite, the smartcard embedded software shall use IC security features and security mechanisms as specified in the smartcard IC documentation (e.g. sensors, ...).

- O.DEV\_TOOLS The smartcard embedded software shall be designed in a secure manner, by using exclusively software development tools (compilers, assemblers, linkers, simulators etc...) and software-hardware integration testing tools (emulators) that will grant the integrity of program and data.

## 4.2.2 **Objectives on phase 2 (development phase)**

- O.SOFT\_ACS Smartcard embedded software shall be accessible only by authorised personnel within the IC designer on the need to know basis.

- O.DESIGN\_ACS IC specifications, detailed design, IC databases, schematics/layout or any further design information shall be accessible only by authorised personnel within the IC designer on the basis of the need to know (physical, personnel, organisational, technical procedures).

- O.DSOFT\_ACS Any IC dedicated software specification, detailed design, source code or any further information shall be accessible only by authorised personnel within the IC design on the need to know basis.

- O.MASK\_FAB Physical, personnel, organisational, technical procedures during photomask fabrication (including deliveries between photomask manufacturer and IC manufacturer) shall ensure the integrity and confidentiality of the TOE.

- O.MECH\_ACS Details of hardware security mechanism specifications shall be accessible only by authorised personnel within the IC designer on the need to know basis.

- O.TI\_ACS Security relevant technology information shall be accessible only by authorised personnel within the IC designer on the need to know basis.

## 4.2.3 **Objectives on phase 3 (manufacturing phase)**

O.TOE\_PRT The manufacturing process shall ensure the protection of the TOE from any kind of unauthorised use such as tampering or theft.

During the IC manufacturing and test operations, security procedures shall ensure the confidentiality and integrity of:

- TOE manufacturing data (to prevent any possible copy, modification, retention, theft or unauthorised use)

- TOE security relevant test programs, test data, databases and specific analysis methods and tools.

These procedures shall define a security system applicable during the manufacturing and test operations to maintain confidentiality of the TOE by control of:

- packaging and storage,

- traceability,

- storage and protection of manufacturing process specific assets (such as manufacturing process documentation, further data, or samples),

- access control and audit to tests, analysis tools, laboratories, and databases,

- change/modification in the manufacturing equipment, management of rejects.

- O.IC\_DLV The delivery procedures from the IC manufacturer shall maintain the integrity and confidentiality of the TOE and its assets.

## 4.2.4 **Objectives on the TOE delivery process (phase 4 to 7)**

O.DLV\_PROTECT Procedures shall ensure protection of TOE material/information under delivery including the following objectives:

- Non-disclosure of any security relevant information,

- Identification of the elements under delivery,

- Meet confidentiality rules (confidentiality level, transmittal form, reception acknowledgement),

- Physical protection to prevent external damage,

- Secure storage and handling procedures are applicable for all TOEs (including rejected TOEs),

- Traceability of TOE during delivery including the following parameters:

- Origin and shipment details,

- Reception, reception acknowledgement,

- Location material/information.

- O.DLV\_AUDIT Procedures shall ensure that corrective actions are taken in case of improper operation in the delivery process (including if applicable any non-conformance to the confidentiality convention) and highlight all non-conformance to this process.

- O.DLV\_RESP Procedures shall ensure that people (shipping department, carrier, reception department) dealing with the procedure for delivery have got the required skill, training and knowledge to meet the procedure requirements and to act to be fully in accordance with the above expectations.

## 4.2.5 **Objectives on phases 4 to 6**

O.TEST\_OPERATE Appropriate functionality testing of the IC shall be used in phases 4 to 6.

During all manufacturing and test operations, security procedures shall be used through phases 4, 5, 6 to maintain confidentiality and integrity of the TOE and of its manufacturing and test data.

#### 4.2.6 **Objectives on phase 7**

- O.USE\_DIAG Secure communication protocols and procedures shall be used between smartcard and terminal.

- O.USE\_SYS The integrity and the confidentiality of sensitive data stored/handled by the system (terminals, communications...) shall be maintained.

# Chapter 5 IT security requirements

63 This part of the ST Lite defines the detailed IT security requirements that shall be satisfied by the TOE or its environment.

## **5.1 TOE** security functional requirements

- 64 The TOE security functional requirements define the functional requirements for the TOE using only functional requirement components drawn from the CC Part 2.

- 65 The minimum strength of function level for the TOE security requirements is SOF-high.

# 5.1.1 Functional Requirements applicable to phase 3 only (testing phase)

## 5.1.1.1 User authentication before any action (FIA\_UAU.2)

66 The TSF shall require each user to be successfully authenticated before allowing any other TSF-mediated actions on behalf of that user.

#### 5.1.1.2 User identification before any action (FIA\_UID.2)

67 The TSF shall require each user to identify itself before allowing any other TSFmediated actions on behalf of that user.

### 5.1.1.3 User attribute definition (FIA\_ATD.1)

68 The TSF shall maintain the following list of security attributes belonging to individual users: **mode\_of\_use**.

## 69 <u>Note</u>: mode\_of\_use has 3 possible values:

- *user mode* : the TOE is in user mode,

- *test mode entry* : transition state for test mode because the user is successfully identified but not authenticated yet,

- *test mode*: the TOE is in test mode.

## 5.1.1.4 TOE security functions testing (FPT\_TST.1)

- 70 The TSF shall run a suite of self-tests **at the conditions that an authorised user** requests it and mode\_of\_use is *test mode*, to demonstrate the correct operation of the TSF.

- 71 The TSF shall provide authorised users with the capability to verify the integrity of TSF data.

- 72 The TSF shall provide authorised users with the capability to verify the integrity of stored TSF executable code.

#### 5.1.1.5 Stored data integrity monitoring (FDP\_SDI.1)

73 The TSF shall monitor user data stored within the TSC for **integrity errors** on all objects, based on the following attributes: **USER\_ROM BIST signature and EEPROM/OTP/OTP2 memory contents**.

| 5.1.2 | Functional require  | ements applicable | to phases 3 to 7 |

|-------|---------------------|-------------------|------------------|

| 5.1.2 | r unctional require | ements applicable | to phases 5 to 7 |

## 5.1.2.1 Management of security functions behaviour (FMT\_MOF.1)

#### 5.1.2.1.1 iteration 1: Unobservability

74 The TSF shall restrict the ability to **modify the behaviour of** the function **of unobservability** to **user and administrator**.

#### 5.1.2.1.2 iteration 2: Testing

- 75 The TSF shall restrict the ability to **disable** the function **of testing** to **administrator**.

- 76 <u>Refinement:</u> once performed, the functions of testing are definitively disabled.

#### 5.1.2.2 Management of security attributes (FMT\_MSA.1)

#### iteration 1: Memory access control

77 The TSF shall enforce the **memory access control SFP** to restrict the ability to **modify** the security attributes **memory\_configuration and memory\_access\_control** to **user**.

#### iteration 2: Testing information flow control

78 The TSF shall enforce the **testing information flow control SFP** to restrict the ability to **modify** the security attributes **test\_type** to **administrator**.

#### 5.1.2.3 Security roles (FMT SMR.1)

- 79 The TSF shall maintain the roles:

- <u>Administrator</u>: user whose associated security attribute mode\_of\_use is set to test mode, so that he has the ability to perform testing operations onto the TOE.

- <u>User</u>: user whose associated security attribute mode\_of\_use is set to user mode.

It can be either an identified user with no test mode privileges or the embedded software.

- 80 The TSF shall be able to associate users with roles.

#### 5.1.2.4 Static attribute initialisation (FMT\_MSA.3)

#### iteration 1: Memory access control

- 81 The TSF shall enforce the **memory access control SFP** to provide **restrictive** default values for security attributes that are used to enforce the security functions policy.

- 82 The TSF shall allow the **user** to specify alternate initial values to override the default values when an object or information is created.

#### iteration 2: Testing information flow control

- 83 The TSF shall enforce the **testing information flow control SFP** to provide **restrictive** default values for security attributes that are used to enforce the security functions policy.

- 84 The TSF shall allow the **administrator** to specify alternate initial values to override the default values when an object or information is created.

## 5.1.2.5 Complete Access Control (FDP\_ACC.2)

- 85 The TSF shall enforce the memory access control SFP on embedded software and IC dedicated software, and all the objects USER\_ROM SOS, USER\_ROM AOS, EEPROM CODE, EEPROM DATA, OTP, RAM, USER\_SFR, TEST\_ROM, OTP2, TEST\_SFR, and all operations among subjects and objects covered by the security functions policy.

- 86 The TSF shall ensure that all operations between any subject in the TSC and any object within the TSC are covered by an access control policy.

#### 5.1.2.6 Security Attribute Based Access Control (FDP\_ACF.1)

87 The TSF shall enforce the **memory access control SFP** to objects based on **mode\_of\_use, memory\_configuration and memory\_access\_control**.

#### 88 <u>Note</u>:

- 1) memory\_configuration splits USER\_ROM into USER\_ROM AOS and USER\_ROM SOS, and EEPROM into EEPROM CODE and EEPROM DATA.

- 2) memory\_access\_control controls data load accesses from EEPROM CODE to EEPROM DATA, from EEPROM CODE to EEPROM CODE, and from EEPROM CODE to USER\_ROM AOS.

The TSF shall enforce the following rules to determine if an operation among controlled subjects and controlled objects is allowed:

Branch accesses from and to memory areas delimited by the memory\_configuration security attribute apply access control rules defined by the following matrix:

|        |                |      |            | Code executed in memory area: |                |                  |  |

|--------|----------------|------|------------|-------------------------------|----------------|------------------|--|

|        |                |      | USER_ROM   | EEPROM                        | USER_SFR / RAM |                  |  |

|        |                |      |            | AOS/SOS                       | CODE           | / other memories |  |

|        | USER_ROM       | AOS  |            | Authorised                    | Authorised     | Prohibited       |  |

| area:  |                | SOS  |            | Authorised                    | Prohibited     | Prohibited       |  |

|        | EEPROM         | CODE | If EEPROM  | Authorised                    | Authorised     | Prohibited       |  |

| lory   |                |      | available  |                               |                |                  |  |

| memory |                |      | Otherwise  | Prohibited                    | Prohibited     | Prohibited       |  |

|        |                | DATA |            | Prohibited                    | Prohibited     | Prohibited       |  |

| h to   |                | OTP  |            | Prohibited                    | Prohibited     | Prohibited       |  |

| Branch | USER_SFR       |      |            | Prohibited                    | Prohibited     | Prohibited       |  |

| Bra    | RAM            |      |            | Prohibited                    | Prohibited     | Prohibited       |  |

|        | Other memories |      | Prohibited | Prohibited                    | Prohibited     |                  |  |

| Table 5.1 - Branch access control matri. | Table 5 | 1 - Branch | 1 access | control | matrix |

|------------------------------------------|---------|------------|----------|---------|--------|

|------------------------------------------|---------|------------|----------|---------|--------|

Data accesses from and to memory areas delimited by the memory\_configuration security attribute apply access control rules defined by the following matrix:

|         |                                   |                                        |            | Code                  | e executed in me | emory area:      |  |  |

|---------|-----------------------------------|----------------------------------------|------------|-----------------------|------------------|------------------|--|--|

|         |                                   |                                        | USER_ROM   | EEPROM                | USER_SFR / RAM   |                  |  |  |

|         |                                   |                                        |            | AOS/SOS               | CODE             | / other memories |  |  |

|         | USER_ROM                          | AOS                                    |            | Authorised            | Conditioned      | Prohibited       |  |  |

| area:   |                                   | SOS                                    |            | Authorised            | Prohibited       | Prohibited       |  |  |

| are     | EEPROM                            | CODEStoreLoadDATAStoreLoadOTPStoreLoad |            | Authorised            | Prohibited       | Prohibited       |  |  |

| ory     |                                   |                                        |            | Authorised            | Conditioned      | Prohibited       |  |  |

| memory  |                                   |                                        |            | Authorised            | Prohibited       | Prohibited       |  |  |

|         |                                   |                                        |            | Authorised            | Conditioned      | Prohibited       |  |  |

| s to    |                                   |                                        |            | Authorised            | Prohibited       | Prohibited       |  |  |

| ess     |                                   |                                        |            | Authorised            | Conditioned      | Prohibited       |  |  |

| acc     | Solution Load Load USER_SFR Store |                                        | Store      | Authorised Prohibited |                  | Prohibited       |  |  |

| te Load |                                   | Authorised                             | Authorised | Prohibited            |                  |                  |  |  |

| D       | RAM                               |                                        | Authorised | Authorised            | Prohibited       |                  |  |  |

|         | Other memorie                     | S                                      |            | Prohibited            | Prohibited       | Prohibited       |  |  |

Table 5.2 - Data access control matrix

The key "Conditioned" means that the access is authorised according to the values contained in the memory\_access\_control attribute

90

- The TSF shall explicitly authorise access of subjects to objects based on the following additional rules:

- The TSF shall explicitly authorise access of IC dedicated software to appropriate memory areas if mode of use is *test mode*.

- The TSF shall explicitly authorise access of IC dedicated software to some TEST\_SFR if mode\_of\_use is *test mode entry*.

89

#### The TSF shall explicitly deny access of subjects to objects based on the rules:

- the TSF shall explicitly deny access of all software to TEST\_ROM and OTP2 if mode\_of\_use is not *test mode*.

- the TSF shall explicitly prohibit write access of all software to NEC OTP area if mode\_of\_use is not *test mode*.

#### 5.1.2.7 Subset Information Flow Control (FDP\_IFC.1)

92 The TSF shall enforce the **testing information flow control SFP** on **the following list of subjects, information and operations**:

| Subjects    | IC dedicated software                      |

|-------------|--------------------------------------------|

| Information | Information in TEST_ROM, OTP2 and TEST_SFR |

| Operations  | Read, Write                                |

Table 5.3 – List of subjects, information and operations for testing information flow control SFP

#### 5.1.2.8 Simple Security Attributes (FDP\_IFF.1)

93

91

The TSF shall enforce the **testing information flow control SFP** based on the following types of subject and information security attributes **command**, **test\_type**, **mode\_of\_use**.

#### Notes:

- 1) "command" represents a well-defined instruction-data exchange.

- 2) "test\_type" specifies several test capabilities of the test software:

- a) TEST ROM mode: this mode mainly allows the user to authenticate himself and select one of the test modes below,

- b) Code execution from the TOE external test software in TEST ROM mode,

- c) Memory Tester mode: this mode is intended to perform EEPROM behavioural tests and to initialise OTP2 area,

- d) ROMless mode: code executed from the TOE external test software with the right to access to all the data,

- e) User ROM BIST mode: code executed from the TOE external test software to check the User ROM BIST signature,

- f) Test ROM BIST mode: code executed from the TOE external test software to check the Test ROM BIST signature,

- g) Peripheral test mode: code executed from the TOE external test software to check the peripheral components (within the TOE) without CPU.

The TSF shall permit an information flow between a controlled subject and controlled information via a controlled operation if the following rules hold:

| Operation | Test type            | Information in TEST_ROM                         |

|-----------|----------------------|-------------------------------------------------|

| Read      | TEST ROM mode        | no command                                      |

|           | Memory Tester mode   | no command                                      |

|           | ROMless mode         | no command                                      |

|           | User ROM BIST mode   | no command                                      |

|           | Test ROM BIST mode   | TEST_ROM check command                          |

|           | Peripheral test mode | no command                                      |

| Write     | All test types       | Note: write operation is impossible in TEST_ROM |

Table 5.4 - TEST\_ROM information flow control

| Operation | Test type            | Information in OTP2             |

|-----------|----------------------|---------------------------------|

| Read      | TEST ROM mode        | no command                      |

|           | Memory Tester mode   | OTP2 information read commands  |

|           | ROMless mode         | no command                      |

|           | User ROM BIST mode   | no command                      |

|           | Test ROM BIST mode   | no command                      |

|           | Peripheral test mode | no command                      |

| Write     | TEST ROM mode        | no command                      |

|           | Memory Tester mode   | OTP2 information write commands |

|           | ROMless mode         | no command                      |

|           | User ROM BIST mode   | no command                      |

|           | Test ROM BIST mode   | no command                      |

|           | Peripheral test mode | no command                      |

Table 5.5 - OTP2 information flow control

| Operation | Test type            | Information in TEST_SFR             |  |  |  |  |  |  |  |

|-----------|----------------------|-------------------------------------|--|--|--|--|--|--|--|

| Read      | TEST ROM mode        | TEST_SFR information read commands  |  |  |  |  |  |  |  |

|           | Memory Tester mode   | TEST_SFR information read commands  |  |  |  |  |  |  |  |

|           | ROMless mode         | TEST_SFR information read commands  |  |  |  |  |  |  |  |

|           | User ROM BIST mode   | no command                          |  |  |  |  |  |  |  |

|           | Test ROM BIST mode   | no command                          |  |  |  |  |  |  |  |

|           | Peripheral test mode | no command                          |  |  |  |  |  |  |  |

| Write     | TEST ROM mode        | TEST_SFR information write commands |  |  |  |  |  |  |  |

|           | Memory Tester mode   | TEST_SFR information write commands |  |  |  |  |  |  |  |

|           | ROMless mode         | TEST_SFR information write commands |  |  |  |  |  |  |  |

|           | User ROM BIST mode   | no command                          |  |  |  |  |  |  |  |

|           | Test ROM BIST mode   | no command                          |  |  |  |  |  |  |  |

|           | Peripheral test mode | no command                          |  |  |  |  |  |  |  |

#### Table 5.6 - TEST\_SFR information flow control

- 95 The TSF shall enforce **none**.

- 96 The TSF shall provide **none**.

- 97 The TSF shall explicitly authorise an information flow based on the following rules: **none**.

- 98 The TSF shall explicitly deny an information flow based on the following rules: Read/Write operations to information stored in TEST\_ROM, OTP2 and TEST\_SFR is forbidden when mode\_of\_use is not *test mode*.

## 5.1.2.9 Potential Violation Analysis (FAU\_SAA.1)

- 99 The TSF shall be able to apply a set of rules in monitoring the audited events and based upon these rules indicate a potential violation of the TOE security policy.

- 100 The TSF shall enforce the following rules for monitoring audited events:

- 1) Accumulation or combination of **auditable events listed below** known to indicate a potential security violation;

| Events indicating a potential security violation | Nature of the violation                             |

|--------------------------------------------------|-----------------------------------------------------|

| UV light exposure                                | Because EEPROM/OTP/OTP2 cells are sensitive         |

|                                                  | to UV light, their exposure may corrupt the data    |

|                                                  | stored in them                                      |

| Out of specification power supply                | Out of specification power supply may cause an      |

|                                                  | abnormal operation or even a damage of the TOE      |

| Out of specification external frequency          | Out of specification external frequency may         |

|                                                  | decrease the efficiency of the RNG                  |

| Abnormal behaviour of EEPROM/OTP/OTP2            | Abnormal behaviour may not guarantee the            |

| erasing or writing voltage                       | correct data erasing or writing                     |

| Forbidden memory access                          | Illegal memory access may lead to jeopardise the    |

|                                                  | secrecy of data stored in EEPROM or modify the      |

|                                                  | behaviour of the TOE by branching to                |

|                                                  | unauthorised areas in USER_ROM                      |

| Physical attack to strategic areas of the TOE    | Physical attacks may jeopardise the contents        |

|                                                  | of strategic areas of the TOE                       |

| Bad user authentication                          | unauthorised access to the TOE may jeopardise       |

|                                                  | the integrity and the confidentiality of the memory |

|                                                  | contents and security mechanisms                    |

#### 2) none

## 5.1.2.10 Unobservability (FPR\_UNO.1)

101 The TSF shall ensure that **unauthorised users** are unable to observe the operation **of critical TOE internal activity** on **any objects** by **the embedded software**.

## 5.1.2.11 Notification of Physical Attack (FPT\_PHP.2)

- 102 The TSF shall provide unambiguous detection of physical tampering that might compromise the TSF.

- 103 The TSF shall provide the capability to determine whether physical tampering with the TOE security function's devices or TOE security function's elements has occurred.

- 104 For the detection devices of UV light exposure, out of specification power supply, out of specification external frequency, bad EEPROM/OTP/OTP2 writing or erasing voltage, and physical modification, the TSF shall monitor the devices and elements and notify the embedded software when physical tampering with the TOE security function's devices or TOE security function's elements has occurred.

## 5.1.2.12 Resistance to Physical Attack (FPT\_PHP.3)

105 The TSF shall resist **the following physical tampering scenarios** to the **following list of TSF devices/elements** by responding automatically such that the TOE security policy is not violated.

| Physical tampering scenarios                                 | List of TSF devices/elements |

|--------------------------------------------------------------|------------------------------|

| Out of specification power supply that may cause an abnormal | All TSF devices/elements     |

| operation or even a damage of the TOE                        |                              |

| Out of specification external frequency                      | RNG                          |

| Physical modifications                                       | All TSF devices/elements     |

#### Table 5.8 - Resistance to physical attack Image: Comparison of the second s

## 5.1.2.13 Cryptographic operation (FCS\_COP.1)

#### 5.1.2.13.1 iteration 1: RSA

106 The TSF shall perform **encryption/decryption** in accordance with a specified cryptographic algorithm **RSA** and cryptographic key sizes **of 1024 bits** that meet the following: **RSAES-PKCS1-v1\_5 encryption scheme (cf. Ref. [7])**.

#### 5.1.2.13.2 iteration 2: DES

107 The TSF shall perform **encryption/decryption** in accordance with a specified cryptographic algorithm **DES** and cryptographic key sizes **of 56 bits** that meet the following: **FIPS PUB 46-2 (cf. Ref. [8])**.

#### Note:

108 Given that the strength of cryptographic algorithms is outside the scope of the CC, the minimum SOF claim (at § 65) does not apply to this requirement.

## **5.2 TOE** security assurance requirements

- 109 The assurance requirements are EAL4 augmented of additional CC Part 3 assurance components listed in the following sections.

- 110 These components are hierarchical ones to the components specified in EAL4.

## 5.2.1 ADV\_IMP.2 Implementation of the TSF

#### **Developer action elements:**

111 The developer shall provide the implementation representation for the entire TSF.

#### **Content and presentation of evidence elements:**

- 112 The implementation representation shall unambiguously define the TSF to a level of detail such that the TSF can be generated without further design decisions.

- 113 The implementation representation shall be internally consistent.

- 114 The implementation representation shall describe the relationship between all portions of the implementation.

#### **Evaluator action elements:**

- 115 The evaluator shall confirm that the information provided meets all requirements for content and presentation of evidence.

- 116 The evaluator shall determine that the implementation representation is an accurate and complete instantiation of the TOE security functional requirements.

## 5.2.2 ALC\_DVS.2 Sufficiency of security measures

#### **Developer action elements:**

117 The developer shall produce development security documentation.

#### **Content and presentation of evidence elements:**

- 118 The development security documentation shall describe all the physical, procedural, personnel, and other security measures that are necessary to protect the confidentiality and integrity of the TOE design and implementation in its development environment.

- 119 The development security documentation shall provide evidence that these security measures are followed during the development and maintenance of the TOE.

- 120 The evidence shall justify that the security measures provide the necessary level of protection to maintain the confidentiality and integrity of the TOE.

#### **Evaluator action elements:**

- 121 The evaluator shall confirm that the information provided meets all requirements for content and presentation of evidence.

- 122 The evaluator shall confirm that the security measures are being applied.

## 5.2.3 AVA\_VLA.4 Highly resistant

#### **Developer action elements:**

- 123 The developer shall perform a vulnerability analysis.

- 124 The developer shall provide vulnerability analysis documentation.

#### **Content and presentation of evidence elements:**

- 125 The vulnerability analysis documentation shall describe the analysis of the TOE deliverables performed to search for ways in which a user can violate the TSP.

- 126 The vulnerability analysis documentation shall describe the disposition of identified vulnerabilities.

- 127 The vulnerability analysis documentation shall show, for all identified vulnerabilities, that the vulnerability cannot be exploited in the intended environment for the TOE.

- 128 The vulnerability analysis documentation shall justify that the TOE, with the identified vulnerabilities, is resistant to obvious penetration attacks.

- 129 The vulnerability analysis documentation shall show that the search for vulnerabilities is systematic.

- 130 The vulnerability analysis documentation shall provide a justification that the analysis completely addresses the TOE deliverables.

#### **Evaluator action elements:**

- 131 The evaluator shall confirm that the information provided meets all requirements for content and presentation of evidence.

- 132 The evaluator shall conduct penetration testing, building on the developer vulnerability analysis, to ensure the identified vulnerabilities have been addressed.

- 133 The evaluator shall perform an independent vulnerability analysis.

- 134 The evaluator shall perform independent penetration testing, based on the independent vulnerability analysis, to determine the exploitability of additional identified vulnerabilities in the intended environment.

- 135 The evaluator shall determine that the TOE is resistant to penetration attacks performed by an attacker possessing a high attack potential.

## 5.3 Security requirements for the IT environment

136 The TOE has no asserted dependencies on the IT environment.

# Chapter 6 TOE summary specification

## 6.1 **TOE** security functions

- 137 This section defines the TOE security functions.

- 138 At the end of the section, a mapping shows how these security functions satisfy the TOE security functional requirements.

## 6.1.1 Test mode entry (SF1)

- 139 SF1 controls the access to test mode. This control is implemented by an identification/authentication procedure.

- 140 If user\_mode\_locking is *true* then test mode is forbidden; mode\_of\_use is automatically set to *user mode*.

- 141 <u>Note</u>: by default, user\_mode\_locking is set to *false*.

- 142 SF1 first checks an identification code:

- 1) If identification succeeds, then mode\_of\_use is set to *test mode entry* and SF1 checks the authentication code:

- a) If authentication succeeds, then mode\_of\_use is set to *test mode*.

- b) If authentication fails, SF1 detects a potential violation and triggers a CPU lock.

- 2) If the identification code does not allow to enter in test mode, then mode\_of\_use is set to *user mode*.

- 143 Both identification and authentication are realised by probabilistic mechanisms. The strength of function claimed for SF1 is SOF-high.

## 6.1.2 Testing (SF2)