# **Crypto Library V2.7 on SmartMX** P5Cx081/ CD041/ CD021/ CD016 V1D

# Security Target Lite

**Evaluation documentation** PUBLIC

BSI-DSZ-CC-0864

| information |                                                                                                                                                                                                |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Info        | Content                                                                                                                                                                                        |

| Keywords    | Security Target Lite, Crypto Library, P5Cx081/ CD041/ CD021/ CD016 V1D                                                                                                                         |

| Abstract    | Security Target Lite for the Crypto Library V2.7on P5Cx081/ CD041/<br>CD021/ CD016 V1D according to the Common Criteria for Information<br>Technology Evaluation (CC) at Level EAL4 augmented. |

|             | The Crypto Library is developed and provided by NXP Semiconductors,<br>Business Unit Identification.                                                                                           |

## Revision history

(Latest Rev : 1.1, 6 Nov 2012)

| Rev | Date        | Description                                 |

|-----|-------------|---------------------------------------------|

| 1.1 | 06-Nov-2012 | derived from full ST Rev 1.1, first release |

# **Contact information**

For additional information, please visit: <u>http://www.nxp.com</u> For sales office addresses, please send an email to: <u>salesaddresses@nxp.com</u>

PUBLIC

# Glossary

| CBC     | Cipher Block Chaining (a block cipher mode of operation)                                                                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CBC-MAC | Cipher Block Chaining Message Authentication Code                                                                                                                                    |

| CC      | Common Criteria Version 3.1                                                                                                                                                          |

| CPU     | Central Processing Unit                                                                                                                                                              |

| DEA     | Data Encryption Algorithm                                                                                                                                                            |

| DES     | Data Encryption Standard                                                                                                                                                             |

| DRNG    | Deterministic Random Number Generator                                                                                                                                                |

| EAL     | Evaluation Assurance Level                                                                                                                                                           |

| ECB     | Electronic Code Book (a block cipher mode of operation)                                                                                                                              |

| ECC     | Elliptic Curve Cryptography                                                                                                                                                          |

| IC      | Integrated circuit                                                                                                                                                                   |

| IT      | Information Technology                                                                                                                                                               |

| MMU     | Memory Management Unit                                                                                                                                                               |

| MX      | Memory eXtension                                                                                                                                                                     |

| n/a     | not applicable                                                                                                                                                                       |

| NDA     | Non Disclosure Agreement                                                                                                                                                             |

| РКС     | Public Key Cryptography                                                                                                                                                              |

| PP      | Protection Profile                                                                                                                                                                   |

| PSW(H)  | Program Status Word (High byte)                                                                                                                                                      |

| SAR     | Security Assurance Requirement                                                                                                                                                       |

| SFR     | as abbreviation of the CC term: Security Functional<br>Requirement, as abbreviation of the technical term of the<br>SmartMX-family: Special Function Register                        |

| SIM     | Subscriber Identity Module                                                                                                                                                           |

| ST      | Security Target                                                                                                                                                                      |

| TOE     | Target of Evaluation.                                                                                                                                                                |

| TRNG    | True Random Number Generator                                                                                                                                                         |

| TSF     | Part of the TOE that realizes the security functionality                                                                                                                             |

| TSFI    | TSF Interface, a means by which external entities (or subjects in the TOE but outside of the TSF) supply data to the TSF, receive data from the TSF and invoke services from the TSF |

| UART    | Universal Asynchronous Receiver and Transmitter                                                                                                                                      |

|         |                                                                                                                                                                                      |

# 1. ST Introduction

This chapter is divided into the following sections: "ST Identification", "TOE overview", "CC Conformance and Evaluation Assurance Level" and "Further Definitions and Explanations".

# **1.1 ST Identification**

This Security Target is for the Common Criteria evaluation of the

#### "Crypto Library V2.7 on SmartMX P5Cx081/ CD041/ CD021/ CD016 V1D"

provided by NXP Semiconductors, Business Unit Identification.

For ease of reading during this Security Target the TOE is often called Crypto Library on SmartMX.

ST Identification: Crypto Library V2.7 on SmartMX P5Cx081/ CD041/ CD021/ CD016 V1D , Rev. 1.1 - 6 Nov 2012

The TOE is a **composite TOE**, consisting of:

### the hardware "NXP SmartMX P5Cx081/ CD041/ CD021/ CD016 V1D Secure Smart Card Controller"

which is used as evaluated platform, and all its Major Configurations (see [10] for details):

- P5CD081V1D

- P5CD021V1D

- P5CN081V1D

- P5CD016V1D

- P5CD041V1D

- and

- The "Crypto Library V2.7", which is built upon this platforms.

This Security Target builds up on the Hardware Security Target [10], which refers to the "NXP P5Cx081/ CD041/ CD021/ CD016 V1D Secure Smart Card Controller" provided by NXP Semiconductors, Business Unit Identification.

# 1.2 TOE overview

## 1.2.1 Introduction

The Hardware Security Target [10] contains in section 1.3 "ST Overview" an introduction about the SmartMX hardware TOE that is considered in the evaluation. The Hardware Security Target includes IC Dedicated Software stored in the ROM provided with the SmartMX hardware platform.

The Crypto Library on SmartMX is a cryptographic library, which provides a set of cryptographic functions that can be used by the Smartcard embedded Software. The cryptographic library consists of several binary packages that are intended to be linked to the Smartcard Embedded Software. The Smartcard Embedded Software developer links the binary packages that he needs to his Smartcard Embedded Software and the whole is subsequently implemented in the User ROM.

The NXP SmartMX smart card processor provides the computing platform and cryptographic support by means of co-processors for the Crypto Library on SmartMX.

The TOE provides the security functionality listed below in addition to the functionality described in the Hardware Security Target [10] for the hardware platform:

#### AES

- The AES algorithm is intended to provide encryption and decryption functionality.

- The following modes of operation are supported for AES: ECB, CBC, CBC-MAC.

#### **DES/ 3DES**

- The Single-DES algorithm can be used as a building block, e.g. to implement a Retail-MAC. However, the Single-DES algorithm alone is not considered to be resistant against attacks with a high attack potential, therefore Single-DES alone must not be used for encryption. See also Note 7 in section 4.1.1.

- The Triple-DES (3DES) algorithm is intended to provide encryption and decryption functionality.

- The following modes of operation are supported for DES and Triple-DES: ECB, CBC, CBC-MAC.

#### RSA

- The RSA algorithm can be used for encryption and decryption as well as for signature generation and signature verification.

- The RSA key generation can be used to generate RSA key pairs.

- The RSA public key computation can be used to compute the public key that belongs to a given private key.

## ECC over GF(p)

- The ECC over GF(p) algorithm can be used for signature generation and signature verification

- The ECC over GF(p) key generation algorithm can be used to generate ECC over GF(p) key pairs.

- The ECC Diffie-Hellman key exchange algorithm can be used to establish cryptographic keys. It can be also used as secure point multiplication.

- Provide secure point addition for Elliptic Curves over GF(p)

#### SHA

The SHA-1, SHA-224 and SHA-256 algorithms can be used for different purposes such as computing hash values in the course of digital signature creation or key derivation.

#### Resistance of cryptographic algorithms against side-channel attacks

The cryptographic algorithms (except SHA) are resistant against Side Channel Attacks, including Simple Power Analysis (SPA), Differential Power Analysis (DPA), Differential Fault Analysis (DFA) and timing attacks. More detail may be found in Table 7.

#### **Random number generation**

The TOE provides access to random numbers generated by a software (pseudo) random number generator and functions to perform the required test of the hardware (true) random number generator.

#### Other security functionality

- · The TOE includes internal security measures for residual information protection.

- The TOE provides a secure copy routine.

Note that the TOE does not restrict access to the functions provided by the hardware: these functions are still directly accessible to the Smartcard embedded Software.

#### 1.2.2 Life-Cycle

The life cycle of the hardware platform as part of the TOE is described in section 1.4.4 "TOE Intended Usage" of the Hardware Security [10]. The delivery process or the hardware platform is independent from the Crypto Library on SmartMX.

The Crypto Library is delivered in Phase 1 (for a definition of the Phases refer to section '1.2.3 TOE life cycle' of the Protection Profile for a definition of the Phases refer to section '1.2.3 TOE life cycle' of the Protection Profile [9]) as a software package (a set of binary files) to the developers of Smartcard Embedded Software. The Smartcard Embedded Software may comprise in this case an operating system and/or other smart card software (applications). The Software developer can incorporate the Crypto Library into their product.

The subsequent use of the Crypto Library by Smartcard Embedded Software Developers is out of the control of the developer NXP Semiconductors, Business Unit Identification; the integration of the Crypto Library into Smartcard Embedded Software is not part of this evaluation.

#### **Security during Development and Production**

The development process of the Crypto Library is part of the evaluation. The access to the implementation documentation, test bench and the source code is restricted to the development team of the Crypto Library on SmartMX. The security measures installed within NXP, including a secure delivery process, ensure the integrity and quality of the delivered Crypto Library binary files.

#### 1.2.3 Specific Issues of Smartcard Hardware and the Common Criteria

Regarding the Application Note 2 of the Protection Profile [9] the TOE provides additional functionality which is not covered in the Protection Profile and the Hardware Security Target [10]. This additional functionality is added using the policy "P.Add-Func" (see section 2.4 of this Security Target).

# 1.3 CC Conformance and Evaluation Assurance Level

The evaluation is based upon:

- Common Criteria for Information Technology Security Evaluation Part 1: Introduction and general model, Version 3.1 Revision 3, July 2009, CCMB-2009-07-001, [1]

- Common Criteria for Information Technology Security Evaluation Part 2: Security functional components, Version 3.1 Revision 3, July 2009, CCMB-2009-07-002, [2]

- Common Criteria for Information Technology Security Evaluation Part 3: Security assurance components, Version 3.1 Revision 3, July 2009, CCMB-2009-07-003, [3]

For the evaluation the following methodology will be used:

Common Criteria for Information Technology Security Evaluation – Evaluation methodology, Version 3.1 Revision 3, July 2009, CCMB-2009-07-004, [4]

The chosen level of assurance is EAL 4 augmented.

The augmentations chosen are:

- ALC\_DVS.2 and

- · AVA\_VAN.5.

This Security Target claims the following CC conformances:

- · CC 3.1 Part 2 extended, Part 3 conformant, EAL 4 augmented

- Conformance to the Protection Profile "Bundesamt für Sicherheit in der Informationstechnik (BSI): Security IC Platform Protection Profile, Version 1.0, 15.06.2007; Registered and Certified by Bundesamt für Sicherheit in der Informationstechnik (BSI) under the reference BSI-PP-0035", [9]

The assurance level for evaluation and the functionality of the TOE are chosen in order to allow the confirmation that the TOE is suitable for use within devices compliant with the German Digital Signature Law.

**Note 1.** The hardware platform is evaluated according to the assurance level EAL 4 augmented. The evaluation of the hardware platform is appropriate for the composite evaluation since both the EAL level and the augmentations claimed in this Security Target are identical to those claimed for the hardware platform (refer to the Hardware Security Target [10]).

# **1.4 TOE Description**

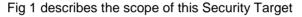

The Target of Evaluation (TOE) consists of a hardware part and a software part:

- · The hardware part consists of the

- NXP P5Cx081/ CD041/ CD021/ CD016 V1D Secure Smart Card Controller

with IC Dedicated Software stored in the Test-ROM that is not accessible in the System Mode or the User Mode after Phase 3. The hardware part of the TOE includes dedicated guidance documentation.

• The software part consists of the IC Dedicated Support Software "Crypto Library V2.7" which consists of a software library and associated documentation. The Crypto Library on SmartMX is an additional part that provides cryptographic functions that can be operated on the hardware platform as described in this Security Target.

The TOE is described in three layers:

- 1. The Protection Profile [9] describes general requirements for smart card controllers and their support software. It is a common basis for smart card platform evaluations and defines the minimum requirements for the TOE hardware and its associated functionality.

- 2. The Hardware Security Target [10] defines the functionality of the platform provided by the SmartMX Smart Card Controller.

- 3. The Crypto Library on SmartMX provides additional functionality to the developer of Smartcard Embedded Software. It is a supplement of the basic cryptographic features provided by the hardware platform. The Crypto Library on SmartMX implements cryptographic algorithms with countermeasures against the attacks described in this Security Target using the co-processors of the SmartMX to provide a software programming interface for the developer of the Smartcard Embedded Software.

The hardware part of the TOE is not described in detail in this document. Details are included in the Hardware Security Target [10] and therefore this latter document will be

cited wherever appropriate. However the assets, assumptions, threats, objectives and security functional requirements are tracked in this Security Target.

The TOE components consist of all the TOE components listed in Table 1 of the Hardware Security Target [10] plus all TOE components listed in the table below:

| Table 1. | Compone | ents of the TOE that ar | e additional to Tab | ole 1 in [10] |

|----------|---------|-------------------------|---------------------|---------------|

|          |         |                         | _                   |               |

| Туре      | Name                                 | Release            | Date               | Form of Delivery    |

|-----------|--------------------------------------|--------------------|--------------------|---------------------|

| Software  | Crypto Library                       | 2.7                | 26 March 2010      | Electronic file     |

| Documents | Guidance<br>Documents<br>[15] - [23] | See reference list | See reference list | Electronic Document |

## 1.4.1 Hardware Description

The NXP SmartMX hardware is described in section 1.4.2.1 "Hardware Description" of the Hardware Security Target [10]. The IC Dedicated Test Software and IC Dedicated Support Software stored in the Test-ROM and delivered with the hardware platform is described in section 1.4.2.2 "Software Description" of the Hardware Security Target [10].

## **1.4.2 Software Description**

A Smartcard embedded Software developer may create Smartcard embedded Software to execute on the NXP SmartMX hardware. This software is stored in the User ROM of the NXP SmartMX hardware and is not part of the TOE, with one exception: the Smartcard embedded Software may contain the Crypto Library on SmartMX (or parts thereof<sup>1</sup>) and this Crypto Library (or parts thereof) is part of the TOE.

The TOE provides  $AES^2$ , DES, Triple-DES (3DES), RSA, RSA key generation, RSA public key computation, ECC over GF(p) signature generation and verification, ECC over GF(p) key generation, ECC Diffie-Helmann key-exchange, SHA-1, SHA-224 and SHA-256 algorithms.

Many of these algorithms are resistant against side-channel attacks: more information may be found in Table 7.

The TOE supports various key sizes for RSA up to a limit of 5024 bits and for ECC over GF(p) up to a limit of 544 bits.

In addition, the Crypto Library implements a software (pseudo) random number generator which is initialized (seeded) by the hardware random number generator of the SmartMX.

Finally, the TOE provides a secure copy routine and includes internal security measures for residual information protection.

These crypto functions are supplied as a library rather than as a monolithic program, and hence a user of the library may include only those functions that are actually required – it is not necessary to include all cryptographic functions of the library in every Smartcard Embedded Software. For example, it is possible to omit the RSA or the SHA-1 components. However, some dependencies exist; details are described in the User Guidance [15].

<sup>2.</sup> AES, DES and Triple-Des can be used in ECB, CBC or CBC-MAC mode.

## 1.4.3 Documentation

The documentation for the NXP SmartMX hardware is listed in section 1.4.2.3 "Documentation" of the Hardware Security Target [10].

The Crypto Library has associated user guidance documentation (see Table 1). This contains:

- the specification of the functions provided by the Crypto Library,

- details of the parameters and options required to call the Crypto Library by the Smartcard Embedded Software and

- user guidelines on the secure usage of the Crypto Library, including the requirements on the environment (the Smartcard Embedded Software calling the Crypto Library is considered to be part of the environment).

## **1.4.4** Interface of the TOE

The interface to the NXP SmartMX hardware is described in section 1.4.5 "Interface of the TOE" of the Hardware Security Target [10]. The use of this interface is not restricted by the use of the Crypto Library on SmartMX.

The interface to the TOE additionally consists of software function calls, as detailed in the "User Guide and Reference" document of the Crypto Library on SmartMX. The developer of the Smartcard Embedded Software will link the required functionality of the Crypto Library on SmartMX into the Smartcard Embedded Software as required for his Application.

## 1.4.5 Life Cycle and Delivery of the TOE

The life cycle and delivery for the NXP SmartMX hardware is described in section 1.4.4 "TOE Intended Usage" of the Hardware Security Target [10]. The crypto library is encrypted and signed for delivery. The actual delivery of the signed, encrypted file may be by e-mail or on physical media such as compact disks.

The Crypto Library is delivered as part of Phase 1 (for a definition of the Phases refer to section '1.2.3 TOE life cycle' of the Protection Profile [9]) to the Smartcard Embedded Software developer. The Smartcard Embedded Software developer then integrates the Crypto Library in the Smartcard Embedded Software.

Delivery of the Crypto Library to the Smartcard Embedded Software developer may be by e-mail or by delivering physical media such as compact disks by mail or courier. To protect the Crypto Library during the delivery process, the Crypto Library is encrypted and digitally signed.

## 1.4.6 TOE Intended Usage

Regarding to phase 7 (for a definition of the Phases refer to section '1.2.3 TOE life cycle' of the Protection Profile [9]), the combination of the smartcard hardware and the Smartcard Embedded Software is used by the end-user. The method of use of the product in this phase depends on the application. The TOE is intended to be used in an unsecured environment, that is, the TOE does not rely on the Phase 7 environment to counter any threat.

PUBLIC

For details on the usage of the hardware platform refer to section 1.4.4 "TOE Intended Usage" in the Hardware Security Target [10].

The Crypto Library on SmartMX is intended to support the development of the Smartcard Embedded Software since the cryptographic functions provided by the Crypto Library on SmartMX include countermeasures against the threats described in this Security Target. The used modules of the Crypto Library on SmartMX are linked to the other parts of the Smartcard Embedded Software and they are implemented as part of the Smartcard Embedded Software in the User ROM of the hardware platform.

## 1.4.7 TOE User Environment

The user environment for the crypto library is the Smartcard Embedded Software, developed by customers of NXP, to run on the NXP SmartMX hardware.

## 1.4.8 General IT features of the TOE

The general features of the NXP SmartMX hardware are described in section 1.3 "TOE overview" of the Hardware Security Target [10]. These are supplemented for the TOE by the functions listed in section 1.2.1 of this Security Target.

# **1.5 Further Definitions and Explanations**

Since the Security Target claims conformance to the Protection Profile [9], the concepts are used in the same sense. For the definition of terms refer to the Protection Profile [9]. This chapter does not need any supplement in the Security Target.

PUBLIC

# 2. Security Problem Definition

This Security Target claims conformance to the Protection Profile [9]. The Assets, Assumptions, Threats and Organizational Security Policies of the Protection Profile are assumed here, together with extensions defined in chapter 3 "Security Problem Definition" of the Hardware Security Target [10]. In the following sub-sections, only extensions to the different sections are listed. The titles of the chapters that are not extended are cited here for completeness.

# 2.1 Description of Assets

Since this Security Target claims conformance to the Protection Profile [9], the assets defined in section 3.1 of the Protection Profile apply to this Security Target.

User Data and TSF data are mentioned as assets in [10]. Since the data computed by the crypto library contains keys, plain text and cipher text that are considered as User Data and e.g. blinding vectors that are considered as TSF data the assets are considered as complete for this Security Target.

# 2.2 Assumptions

Since this Security Target claims conformance to the Protection Profile [9], the assumptions defined in section 3.2 of the Protection Profile, described in section 3.4 "Assumptions" of the Hardware Security Target [10] and shown in Table 2, are valid for this Security Target.

## Table 2. Assumptions defined in the PP [9] and the Hardware Security Target

| Name             | Title                                                           | Defined in |

|------------------|-----------------------------------------------------------------|------------|

| A.Process-Sec-IC | Protection during Packaging, Finishing and Personalization      | PP [9]     |

| A.Plat-Appl      | Usage of Hardware Platform                                      | PP [9]     |

| A.Resp-Appl      | Treatment of User Data                                          | PP [9]     |

| A.Check-Init     | Check of initialization data by the Smartcard Embedded Software | HW-ST [10] |

| A.Key-Function   | Usage of Key-dependent Functions                                | HW-ST [10] |

This Security Target defines one additional assumption:

A.RSA-Key-Gen Operational Environment for RSA Key Generation function

The RSA Key Generation provides two different modes. The insecure mode is not secured against side-channel attacks. Therefore the execution speed is faster than in the secure mode. When this version is executed the environment has to avoid side-channel attacks.

# 2.3 Threats

Since this Security Target claims conformance to the Protection Profile [9], the threats defined in section 3.2 of the Protection Profile, described in section 3.2 "Threats" of the Hardware Security Target [10] and shown in Table 3, are valid for this Security Target.

| Table 3. | Threats defined in the Protection Profile |  |

|----------|-------------------------------------------|--|

| Namo     | Title                                     |  |

| Name                | Title                                   | Defined in |

|---------------------|-----------------------------------------|------------|

| T.Leak-Inherent     | Inherent Information Leakage            | PP [9]     |

| T.Phys-Probing      | Physical Probing                        | PP [9]     |

| T.Malfunction       | Malfunction due to Environmental Stress | PP [9]     |

| T.Phys-Manipulation | Physical Manipulation                   | PP [9]     |

| T.Leak-Forced       | Forced Information Leakage              | PP [9]     |

| T.Abuse-Func        | Abuse of Functionality                  | PP [9]     |

| T.RND               | Deficiency of Random Numbers            | PP [9]     |

Note 2. Within the Hardware Security Target [10] the threat T.RND has been used in a context where the hardware (true) random number generator is threatened. The TOE consists of both hardware (NXP SmartMX) and software (Crypto Library on SmartMX). The Crypto Library provides random numbers generated by a software (pseudo) random number generator. Therefore the threat T.RND explicitly includes both deficiencies of hardware random numbers as well as deficiency of software random numbers.

# 2.4 Organizational Security Policies

Since this Security Target claims conformance to the Protection Profile [9], the Policy P.Process-TOE "Protection during TOE Development and Production" of the Protection Profile is applied here also.

The hardware security target defines the following additional security policies:

#### P.Add-Components: Additional Specific Security Components

The SmartMX processor part of the TOE provides the following additional security functionality to the Smartcard Embedded Software:

- Triple-DES encryption and decryption

- · AES encryption and decryption

- Area based Memory Access Control

- Memory separation for different software parts (including IC Dedicated Software and Security IC Embedded Software)

- Special Function Register Access Control

The Crypto Library part of the TOE uses the Triple-DES co-processor hardware to provide DES security functionality, as listed below in P.Add-Func: Additional Specific Security Functionality.

PUBLIC

The Crypto Library makes no use of either the Area based Memory Access Control or the Special Function Register Access Control. These features are for the use and control of the Smartcard Embedded Software that includes the Crypto Library.

In addition to the security functionality provided by the hardware mentioned above and defined in the Security Target of the SmartMX, the following additional security functionality is provided by the Crypto Library for use by the Smart Card Embedded Software:

#### P.Add-Func: Additional Specific Security Functionality

The TOE provides the following additional security functionality to the Smartcard Embedded Software:

- · AES encryption and decryption

- Triple-DES<sup>3</sup> encryption and decryption,

- · RSA encryption, decryption, signature generation and verification,

- · RSA public key computation

- · RSA key generation,

- · ECC over GF(p) signature generation and encryption,

- ECC over GF(p) key generation,

- · ECC Diffie-Hellman key exchange

- ECC Secure Point Addition

- · SHA-1, SHA-224 and SHA-256 Hash Algorithms,

- access to the RNG (implementation of a software RNG and tests for the hardware RNG),

- · secure copy routine.

In addition, the TOE shall

- · provide protection of residual information, and

- provide resistance against side channel attacks as described in Table 7 and in section 5.1.13 F.COPY.

Regarding the Application Note 12 of the Protection Profile [9] there are no other additional policies defined in this Security Target.

<sup>3.</sup> See also Note 7 in section 4.1.1.

# 3. Security Objectives

This chapter contains the following sections: "Security Objectives for the TOE" and "Security Objectives for the Operational environment".

## 3.1 Security Objectives for the TOE

The following table lists the security objectives of the Protection Profile [9] and the Hardware Security Target [10].

Table 4.

Security Objectives defined in the Protection Profile and the Hardware Security

Target

| Name                | Title                                           | Defined in |

|---------------------|-------------------------------------------------|------------|

| O.Leak-Inherent     | Protection against Inherent Information Leakage | PP [9]     |

| O.Phys-Probing      | Protection against Physical Probing             | PP [9]     |

| O.Malfunction       | Protection against Malfunctions                 | PP [9]     |

| O.Phys-Manipulation | Protection against Physical Manipulation        | PP [9]     |

| O.Leak-Forced       | Protection against Forced Information Leakage   | PP [9]     |

| O.Abuse-Func        | Protection against Abuse of Functionality       | PP [9]     |

| O.Identification    | TOE Identification                              | PP [9]     |

| O.RND               | Random Numbers                                  | PP [9]     |

| O.HW_DES3           | Triple DES Functionality                        | HW-ST [10] |

| O.HW_AES            | AES Functionality                               | HW-ST [10] |

| O.MF_FW             | MIFARE Firewall                                 | HW-ST [10] |

| O.MEM_ACCESS        | Area based Memory Access Control                | HW-ST [10] |

| O.SFR_ACCESS        | Special Function Register Access Control        | HW-ST [10] |

**Note 3.** Within the Hardware Security Target [10] the objective O.RND has been used in context with the hardware (true) random number generator (RNG). In addition to this, the TOE (Crypto Library on SmartMX) also provides a software (pseudo) RNG and implements test routines for the hardware RNG. Therefore the objective O.RND is extended to comprise also the quality of random numbers generated by the software (pseudo) RNG. See also Note 2 in section 2.3, which extends T.RND in a similar way.

The following additional security objectives are defined by this ST, and are provided by the software part of the TOE:

| The TOE includes functionality to provide encryption and decryption facilities of the AES algorithm, resistant to attack as listed in Table 7.                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The TOE includes functionality to provide encryption and decryption facilities of the Triple-DES algorithm, resistant to attack as listed in. (see also Note 7 in section 4.1.1).                               |

| The TOE includes functionality to provide encryption,<br>decryption, signature creation and signature verification using<br>the RSA algorithm, resistant to attack as listed in Table 7.                        |

| The TOE includes functionality to compute an RSA public key from an RSA private key, resistant to attack as listed in Table 7.                                                                                  |

| The TOE includes functionality to generate RSA key pairs, resistant to attack as listed in Table 7.                                                                                                             |

| The TOE includes functionality to provide signature creation<br>and signature verification as well as secure point addition<br>using the ECC over GF(p) algorithm, resistant to attack as<br>listed in Table 7. |

| The TOE includes functionality to provide Diffie-Hellman key exchange based on ECC over GF(p), resistant to attack as listed in Table 7.                                                                        |

| The TOE includes functionality to generate ECC over GF(p) key pairs, resistant to attack as listed in Table 7.                                                                                                  |

| The TOE includes functionality to provide electronic hashing facilities using the SHA-1, SHA-224 and SHA-256 algorithms.                                                                                        |

| The TOE includes functionality to copy memory content using<br>a routine that implements countermeasures against side<br>channel attacks.                                                                       |

| The TOE includes measures to ensure that the memory resources being used by the TOE cannot be disclosed to subsequent users of the same memory resource.                                                        |

|                                                                                                                                                                                                                 |

# 3.2 Security Objectives for the Operational environment

The security objectives for the operational environment, listed in the following Table 5, are taken from the PP [9]. Additional refinements in the Hardware Security Target [10] are also valid in the ST for the Crypto Library (the "IC Dedicated Support Software").

| Table 5. Security 0 | bjectives for the operational enviro                          | onment                              |

|---------------------|---------------------------------------------------------------|-------------------------------------|

| Name                | Title                                                         | Applies to phase                    |

| OE.Plat-Appl        | Usage of Hardware Platform                                    | Phase 1                             |

| OE.Resp-Appl        | Treatment of User Data                                        | Phase 1                             |

| OE.Process-Sec-IC   | Protection during Packaging,<br>Finishing and Personalization | Phase 4 through delivery to phase 7 |

Table 5.

Security Objectives for the operational environment

The crypto library TOE assumes that the Smartcard Embedded Software abides by the provisions detailed in "Clarification of "Usage of Hardware Platform (OE.Plat-Appl)" and "Clarification of Treatment of User Data (OE.Resp-Appl)" contained within section 4.2 "Security Objectives for the Operational environment" of the Hardware Security Target [10].

The Hardware Security Target [10] defines, in section 4.3 "Security Objectives for the Operational environment", the following additional security objective for the Smart Card Embedded Software:

| OE.Check-Init | Check of initialization data by the Smart Card Embedded |

|---------------|---------------------------------------------------------|

|               | Software.                                               |

This Security Target defines additional security objectives for the operational environment:

| OE.RSA-Key-Gen | In case that resistance of the fast, but insecure mode of the |

|----------------|---------------------------------------------------------------|

|                | RSA Key Generation against side channel attacks is needed,    |

|                | the operational environment shall ensure that side-channel    |

|                | attacks cannot be performed.                                  |

# 4. Security Requirements

## 4.1 Security Functional Requirements

To support a better understanding of the combination Protection Profile and Security Target of the hardware platform vs. this Security Target (Crypto Library on SmartMX), the TOE SFRs are presented in the following two different sections.

#### 4.1.1 SFRs of the Protection Profile and the Security Target of the platform

The Security Functional Requirements (SFRs) for this TOE (Crypto Library on SmartMX) are specified based on the Smart Card IC Platform Protection Profile [9], and are defined in the Common Criteria or in the Protection Profile, as is shown by the third column of the following table:

| Name      | Title                                       | Defined in                                                                                                    |

|-----------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| FAU_SAS.1 | Audit storage                               | PP Section 5.3 [9]<br>(provided by chip HW)                                                                   |

| FCS_RNG.1 | Generation of random numbers                | PP [9] Section 5.1                                                                                            |

| FDP_IFC.1 | Subset information flow control             | CC Part 2 [2]<br>(provided partly by chip HW and<br>partly by crypto library SW, see the<br>following Note 4) |

| FDP_ITT.1 | Basic internal transfer protection          | CC Part 2 [2]<br>(provided partly by chip HW and<br>partly by crypto library SW, see the<br>following Note 4) |

| FMT_LIM.1 | Limited capabilities                        | PP Section 5.2 [9]<br>(provided by chip HW)                                                                   |

| FMT_LIM.2 | Limited availability                        | PP Section 5.2 [9]<br>(provided by chip HW)                                                                   |

| FPT_FLS.1 | Failure with preservation of secure state   | CC Part 2 [2]<br>(provided by chip HW)                                                                        |

| FPT_ITT.1 | Basic internal TSF data transfer protection | CC Part 2 [2]<br>(provided partly by chip HW and<br>partly by crypto library SW, see the<br>following Note 4) |

| FPT_PHP.3 | Resistance to physical attack               | CC Part 2 [2]<br>(provided by chip HW)                                                                        |

| FRU_FLT.2 | Limited fault tolerance                     | CC Part 2 [2]<br>(provided by chip HW)                                                                        |

Table 6.

SFRs defined in the Protection Profile or the Common Criteria

These requirements have already been stated in the hardware ST [10] and are fulfilled by the chip hardware, if not indicated otherwise in Table 6. See also the following Note 4.

- Note 4. Refinement: The functional requirements FDP\_ITT.1, FPT\_ITT.1 and FDP\_IFC.1 are refined for this composite evaluation to also include resistance against leakage (SPA, DPA, Timing attacks)<sup>4</sup> of secret information during the application of: AES, DES, 3DES, RSA, RSA key generation, RSA public key computation, ECC over GF(p), ECC Point Addition, ECC Diffie-Hellman Key Exchange and ECC over GF(p) key generation. Compared to the Hardware Security Target [10] the text of these requirements remains unchanged, but these requirements now apply to a more comprehensive TOE (including hardware and software). See also the following Note 6 for a discussion of DFA resistance. FDP\_IFC.1 is again refined to include also resistance against leakage for the secure copy routine (see also section 5.1.13 F.COPY as well as the requirements FDP\_ITT.1[COPY] and FPT\_ITT.1[COPY] in section 4.1.2)<sup>5</sup>.

- Note 5. Refinement: FPT\_FLS.1 is refined as compared to its first definition in the PP [9] and its instantiation in the hardware ST [10] to include not only the hardware sensors but also "software sensors" that detect DFA attacks on AES, DES, 3DES, RSA and ECC over GF(p) computations. Therefore the requirement is repeated here together with the extended refinement. FPT\_FLS.1 now includes also DFA protection for AES, DES, 3DES, RSA and ECC over GF(p). Note, that FRU\_FLT.2, which is not modified, works closely together with FPT\_FLS.1.

The TOE shall meet the requirements "Random number generation" and "Failure with preservation of secure state (FPT\_FLS.1)" as specified below.

## FCS\_RNG.1[DET] Random number generation

The hardware part of the TOE (NXP SmartMX) provides a physical random number generator (RNG) that fulfils FCS\_RNG.1 as already mentioned above in Table 6. The additional software part of the TOE (Crypto Library) implements a software (pseudo) RNG that fulfils FCS\_RNG.1[DET] (see below). This software RNG obtains its seed from the hardware RNG, after the TOE (Crypto Library) has performed a self test of the hardware RNG.

| Hierarchical to:   | No other components.                                                                                                                                                                                                                                                                                                                        |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCS_RNG.1.1[DET]   | The TSF shall provide a <i>deterministic</i> <sup>6</sup> random number generator that implements a <i>chi-squared test on the seed generator.</i>                                                                                                                                                                                          |

| FCS_RNG.1.2[DET]   | The TSF shall provide random numbers that meet class K.4 of AIS20 [5].                                                                                                                                                                                                                                                                      |

| Application Notes: | The Crypto Library on SmartMX provides the smartcard<br>embedded software with separate library calls to initialize the<br>random number generator (which includes the chi-squared<br>test) and to generate random data. It is the responsibility of<br>the user to initialize the random number generator before<br>generating random data |

| Dependencies:      | No dependencies.                                                                                                                                                                                                                                                                                                                            |

4. see also Table 7 Algorithm Resistance Overview

FDP\_ITT.1 and FPT\_ITT.1 are iterated in order to allow more exact mappings (see FDP\_ITT.1[COPY] and FPT\_ITT.1[COPY] in section 4.1.2), but they still refer to the same information flow control policy, i.e. FDP\_IFC.1 is not iterated.

<sup>&</sup>lt;sup>6</sup> Implemented through a recursive call of 2-key triple-DES

PUBLIC

| Note: | Only if the chi-squared test succeeds the hardware RNG seeds the software RNG implemented as part of the Crypto Library on SmartMX (as part of security functionality F.RNG_Access). |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | The Crypto Library does not prevent the operating system from accessing the hardware RNG. If the hardware RNG is                                                                     |

from accessing the hardware RNG. If the hardware RNG is used by the operating system directly, it has to be decided based on the Smartcard Embedded Software's security needs, what kind of test has to be performed and what requirements will have to be applied for this test. In this case the developer of the Smartcard Embedded Software must ensure that the conditions prescribed in the Guidance, Delivery and Operation Manual for the NXP SmartMX Secure Smart Card Controller are met.

#### FPT\_FLS.1 Failure with preservation of secure state

| Hierarchical to: | No other components.                                                                                                                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPT_FLS.1.1      | The TSF shall preserve a secure state when the following types of failures occur: <i>(i) exposure to operating conditions which may not be tolerated according to the requirement Limited fault tolerance (FRU_FLT.2) and where therefore a malfunction could occur and (ii) DFA attacks on AES, DES, 3DES, RSA and ECC over GF(p).</i> |

| Dependencies:    | No dependencies                                                                                                                                                                                                                                                                                                                         |

| Refinement:      | The term "failure" above also covers "circumstances". The TOE prevents failures for the "circumstances" defined above.                                                                                                                                                                                                                  |

**Note 6.** This refinement should be understood with the following implementation details in mind: The TOE contains both hardware sensors (implemented in the chip card hardware) and software sensors (implemented in the Crypto Library software). The software sensors detect DFA attacks in AES, DES, 3DES, RSA and ECC over GF(p) computations and this detection leads to a secure state (no computation results are output and an exception is thrown) in case such an attack occurs. The Smartcard Embedded Software is expected to handle this exception and further ensure a secure state.

The properties of the cryptographic algorithms in respect to their resistance<sup>7</sup> against Side Channel Analysis (FDP\_ITT.1, FPT\_ITT.1, FDP\_IFC.1, FPT\_FLS.1) can be summarized as follows:

| Algorithm                                                         | Resistant against |     |     |     |  |

|-------------------------------------------------------------------|-------------------|-----|-----|-----|--|

| AES                                                               | Timing            | SPA | DPA | DFA |  |

| DES                                                               | Timing            | SPA | DPA | DFA |  |

| 3DES                                                              | Timing            | SPA | DPA | DFA |  |

| RSA encryption, decryption, signature generation and verification | Timing            | SPA | DPA | DFA |  |

#### Table 7. Algorithm Resistance Overview

7. SPA = Simple Power Analysis, DPA = Differential Power Analysis, DFA = Differential Fault Analysis

PUBLIC

| Algorithm                       | Resistant ag | gainst |     |     |

|---------------------------------|--------------|--------|-----|-----|

| RSA Public Key Computation      | Timing       | SPA    | n/a | n/a |

| RSA Key Generation              | Timing       | SPA    | n/a | n/a |

| ECC over GF(p)                  | Timing       | SPA    | DPA | DFA |

| ECC Diffie-Hellman Key Exchange | Timing       | SPA    | DPA | n/a |

| ECC over GF(p) Key Generation   | Timing       | SPA    | n/a | n/a |

| SHA-1, SHA-224 and SHA-256      | -            | -      | n/a | n/a |

The abbreviation "n/a" in Table 7 Algorithm Resistance Overview means "not applicable", i.e. the TOE does not provide countermeasures here. This does not mean that the algorithm is insecure; rather at the time of writing this Security Target no promising attacks were known.

- Note 7. The countermeasures that protect 3DES against side channel attacks also protect the Single-DES algorithm against these kinds of attacks. Therefore side channel resistance is also claimed for Single-DES. However, it must be noted that Single-DES is no longer considered to be resistant against attackers with a high attack potential, therefore Single-DES must not be used as an encryption algorithm without any additional protection. For the evaluated TOE, Single-DES does not constitute a security functionality on its own. The resistance of Single-DES and Triple-DES against side channel attacks protects the confidentiality of the keys used in all modes of operation (ECB, CBC, CBC-MAC).

- **Note 8.** The protection of the RSA Key Generation against attacks is only given if the secure mode is executed or if the insecure mode is executed in a secure environment.

- **Note 9.** DPA resistance for ECC Diffie-Hellman Key Exchange is only given with respect to the private key, not for the public key. This is of interest when using the function for a secure point multiplication. In this case only the scalar is protected against DPA like attacks, but not the point.

The SFRs from Table 6 are supplemented by additional SFRs, defined in the Common Criteria, as described in sections 6.1.2 "Additional SFRs regarding cryptographic functionality" and 6.1.3 "Additional SFRs regarding access control" of the Hardware Security Target[10] and shown in the following table.

| Name           | Title                   | Defined in                                                                                                                          |

|----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| FCS_COP.1[AES] | Cryptographic operation | CC Part 2 [2], and added to PP in the<br>Hardware ST [10] section 6.1.2 "Additional<br>SFRs regarding cryptographic functionality". |

| FCS_COP.1[DES] | Cryptographic operation | CC Part 2 [2], and added to PP in the<br>Hardware ST [10] section 6.1.2 "Additional<br>SFRs regarding cryptographic functionality". |

| FDP_ACC.1[MEM] | Subset access control   | CC Part 2 [2], and added to PP in the<br>Hardware ST [10] section 6.1.3 "Additional                                                 |

Table 8. SFRs defined in the Hardware Security Target

PUBLIC

| Name           | Title                                   | Defined in                                                                                                              |

|----------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|                |                                         | SFRs regarding access control".                                                                                         |

| FDP_ACC.1[SFR] | Subset access control                   | CC Part 2 [2], and added to PP in the<br>Hardware ST [10], section 6.1.3 "Additional<br>SFRs regarding access control". |

| FDP_ACF.1[MEM] | Security attribute based access control | CC Part 2 [2], and added to PP in the<br>Hardware [10], section 6.1.3 "Additional<br>SFRs regarding access control".    |

| FDP_ACF.1[SFR] | Security attribute based access control | CC Part 2 [2], and added to PP in the<br>Hardware ST [10], section 6.1.3 "Additional<br>SFRs regarding access control". |

| FMT_MSA.3[MEM] | Static attribute initialization         | CC Part 2 [2], and added to PP in the<br>Hardware ST [10], section 6.1.3 "Additional<br>SFRs regarding access control". |

| FMT_MSA.3[SFR] | Static attribute initialization         | CC Part 2 [2], and added to PP in the<br>Hardware ST [10], section 6.1.3 "Additional<br>SFRs regarding access control". |

| FMT_MSA.1[MEM] | Management of security attributes       | CC Part 2 [2], and added to PP in the<br>Hardware ST [10], section 6.1.3 "Additional<br>SFRs regarding access control". |

| FMT_MSA.1[SFR] | Management of security attributes       | CC Part 2 [2], and added to PP in the<br>Hardware ST [10], section 6.1.3 "Additional<br>SFRs regarding access control". |

| FMT_SMF.1      | Specification of management functions   | CC Part 2 [2], and added to PP in the<br>Hardware ST [10], section 6.1.3 "Additional<br>SFRs regarding access control". |

Like the requirements already listed in Table 6, the requirements listed in Table 8 have already been stated in the Hardware Security Target [10] and are fulfilled by the chip hardware.

## 4.1.2 Additional SFRs

The SFRs in Table 6 and Table 8 are further supplemented by the additional SFRs described in the following subsections of this Security Target, as listed in Table 9. The SFRs described in Table 9 together with the extensions of FDP\_ITT.1, FPT\_ITT.1, FDP\_IFC.1 and FPT\_FLS.1 form the set of SFRs that are new for the crypto library. The composite TOE, consisting of chip hardware and crypto library software, fulfils all requirements from Table 6, Table 8 and Table 9.

| Table 9. | SFRs | defined in | this | Security | Target |

|----------|------|------------|------|----------|--------|

|----------|------|------------|------|----------|--------|

| Name              | Title                          | Defined in                                      |

|-------------------|--------------------------------|-------------------------------------------------|

| FCS_COP.1[SW-AES] | Cryptographic operation (AES)  | CC Part 2 [2]; specified in this ST, see below. |

| FCS_COP.1[SW-DES] | Cryptographic operation (TDES) | CC Part 2 [2]; specified in this ST, see below. |

PUBLIC

| Name                   | Title                                                                          | Defined in                                      |

|------------------------|--------------------------------------------------------------------------------|-------------------------------------------------|

| FCS_COP.1[RSA_encrypt] | Cryptographic operation (RSA encryption and decryption)                        | CC Part 2 [2]; specified in this ST, see below. |

| FCS_COP.1[RSA_public]  | Cryptographic operation (RSA public key computation)                           | CC Part 2 [2]; specified in this ST, see below. |

| FCS_COP.1[RSA_sign]    | Cryptographic operation (RSA signature generation and verification)            | CC Part 2 [2]; specified in this ST, see below. |

| FCS_COP.1[ECC_GF_p]    | Cryptographic operation (ECC over GF(p) signature generation and verification) | CC Part 2 [2]; specified in this ST, see below. |

| FCS_COP.1[ECC_ADD]     | Cryptographic operation (ECC over GF(p) point addition)                        | CC Part 2 [2]; specified in this ST, see below. |

| FCS_COP.1[ECC_DHKE]    | Cryptographic operation (ECC<br>Diffie-Hellman key exchange)                   | CC Part 2 [2]; specified in this ST, see below. |

| FCS_COP.1[SHA]         | Cryptographic operation (SHA-1, SHA-224 and SHA-256)                           | CC Part 2 [2]; specified in this ST, see below. |

| FCS_CKM.1[RSA]         | Cryptographic key generation (RSA key generation)                              | CC Part 2 [2]; specified in this ST, see below. |

| FCS_CKM.1[ECC_GF_p]    | Cryptographic key generation<br>(ECC over GF(p) key<br>generation)             | CC Part 2 [2]; specified in this ST, see below. |

| FCS_CKM.4              | Cryptographic Key Destruction                                                  | CC Part 2 [2]; specified in this ST, see below. |

| FDP_RIP.1              | Subset residual information protection                                         | CC Part 2 [2]; specified in this ST, see below. |

| FDP_ITT.1[COPY]        | Basic internal (user data) transfer protection                                 | CC Part 2 [2]; specified in this ST, see below. |

| FPT_ITT.1[COPY]        | Basic internal TSF data transfer protection                                    | CC Part 2 [2]; specified in this ST, see below. |

|                        |                                                                                |                                                 |

The requirements listed in Table 9 are detailed in the following sub-sections.

#### Additional SFR regarding cryptographic functionality

The TSF provides cryptographic functionality to help satisfy several high-level security objectives. In order for a cryptographic operation to function correctly, the operation must be performed in accordance with a specified algorithm and with a cryptographic key of a specified size. The following Functional Requirements to the TOE can be derived from this CC component:

#### FCS\_COP.1[SW-AES] Cryptographic operation

Hierarchical to:

No other components.

FCS\_COP.1.1[SW-AES]

The TSF shall perform *encryption and decryption* in accordance with the specified cryptographic algorithm AES in one of the following modes of operation: ECB, CBC or CBC

PUBLIC

MAC and cryptographic key sizes 128, 192 and 256 bit that meet the following: FIPS Publication 197, Advanced Encryption Standard (AES), NIST Special Publication 800-38A, 2001 (ECB and CBC mode) and ISO 9797-1, Algorithm 1 (CBC-MAC mode).

Dependencies: [FDP\_ITC.1 Import of user data without security attributes, or FDP\_ITC.2 Import of user data with security attributes, or FCS\_CKM.1 Cryptographic key generation] FCS\_CKM.4 Cryptographic key destruction.

## FCS\_COP.1[SW-DES] Cryptographic operation

|                                                | .)preg.ap.ne eperation                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Hierarchical to:                               | No other components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| FCS_COP.1.1[SW-DES]                            | The TSF shall perform <i>encryption and decryption</i> in accordance with the specified cryptographic algorithm <i>Triple-DES in one of the following modes of operation: ECB, CBC or CBC-MAC</i> and cryptographic key sizes <i>double-length (112 bit) or triple-length (168 bit)</i> that meet the following: <i>ANSI X9.52-1998 [33] (ECB and CBC mode) and FIPS PUB 81 [32] (ECB and CBC mode) and FIPS PUB 81 [32] (ECB and CBC mode) and ISO 9797-1 [27], Algorithm 1 (CBC-MAC mode).</i> |  |

| Application Notes:                             | (1) The TOE also implements Single-DES. For AVA_VAN.5 it is not considered sufficient. Therefore Single-DES is not listed here.                                                                                                                                                                                                                                                                                                                                                                  |  |

|                                                | (2) The CBC mode is to be understood as "outer" CBC mode,<br>i.e. CBC mode as defined in [32] and [33] applied to the block<br>cipher algorithm (either DES or Triple-DES). The CBC-MAC<br>mode of operation as defined in ISO 9797-1 [27], Algorithm 1,<br>and also described in Appendix F of [32] is similar to CBC<br>mode, but the output of the CBC-MAC is restricted to the<br>output of the last Triple-DES operation, i.e. only the last block<br>of the ciphertext is returned.        |  |

| Dependencies:                                  | [FDP_ITC.1 Import of user data without security attributes, or<br>FDP_ITC.2 Import of user data with security attributes, or<br>FCS_CKM.1 Cryptographic key generation]<br>FCS_CKM.4 Cryptographic key destruction.                                                                                                                                                                                                                                                                              |  |

| FCS_COP.1[RSA_encrypt] Cryptographic operation |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Hierarchical to:                               | No other components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| FCS_COP.1.1[RSA_encr                           | ypt] The TSF shall perform <i>encryption and decryption</i> in<br>accordance with the specified cryptographic algorithm <i>RSA</i><br><i>without or with EME-OAEP encoding method</i> and<br>cryptographic key sizes 1536 bits to 5024 bits that meet the<br>following: <i>PKCS #1, v2.1 (RSAEP, RSADP, RSAES-OAEP)</i> .                                                                                                                                                                        |  |

| Application Notes:                             | The TOE also supports key lengths of 256 to 1535 bits. For AVA_VAN.5 these are not considered sufficient. Therefore only keys of at least 1536 bits are listed here.                                                                                                                                                                                                                                                                                                                             |  |

| Dependencies:                                  | [FDP_ITC.1 Import of user data without security attributes, or FDP_ITC.2 Import of user data with security attributes, or                                                                                                                                                                                                                                                                                                                                                                        |  |

PUBLIC

FCS\_CKM.1 Cryptographic key generation] FCS\_CKM.4 Cryptographic key destruction.

## FCS\_COP.1[RSA\_sign] Cryptographic operation

| Hierarchical to:     | No other components.                                                                                                                                                                                                                                                                                                     |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCS_COP.1.1[RSA_sign | ] The TSF shall perform <i>signature generation and verification</i> in accordance with the specified cryptographic algorithm <i>RSA without or with EMSA-PSS encoding method</i> and cryptographic key sizes <i>1536 bits to 5024 bits</i> that meet the following: <i>PKCS #1, v2.1 (RSASP1, RSAVP1, RSASSA-PSS)</i> . |

| Application Notes:   | The TOE also supports key lengths of 256 to 1535 bit. For AVA_VAN.5 these are not considered sufficient. Therefore only keys of least 1536 bits are listed here.                                                                                                                                                         |

| Dependencies:        | [FDP_ITC.1 Import of user data without security attributes, or<br>FDP_ITC.2 Import of user data with security attributes, or<br>FCS_CKM.1 Cryptographic key generation]<br>FCS_CKM.4 Cryptographic key destruction.                                                                                                      |

# FCS\_COP.1[RSA\_public] Cryptographic operation

| Hierarchical to:      | No other components.                                                                                                                                                                                                                                                                |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCS_COP.1.1[RSA_publi | c] The TSF shall perform <i>public key computation</i> in accordance with the specified cryptographic algorithm RSA and cryptographic key sizes 1536 bits to 2048 bits (Straight Forward) or 1536 to 4096 bits (CRT) that meet the following: <i>PKCS #1, v2.1 (RSAEP, RSAVP1).</i> |

| Application Notes:    | (1) The TOE also supports key lengths of 256 to 1535 bits.<br>For AVA_VAN.5 these are not considered sufficient. Therefore<br>only keys of at least 1536 bits are listed here.                                                                                                      |

|                       | (2) The computation will result in the generation of a public RSA key from the private key. As this key is implied by the private key, this is not true key generation, and, to prevent duplication in this ST, this has not been included as a separate FCS_CKM.1 SFR.             |

| Dependencies:         | [FDP_ITC.1 Import of user data without security attributes, or<br>FDP_ITC.2 Import of user data with security attributes, or<br>FCS_CKM.1 Cryptographic key generation]<br>FCS_CKM.4 Cryptographic key destruction.                                                                 |

|                       | Crumtegraphic exercises                                                                                                                                                                                                                                                             |

# FCS\_COP.1[ECC\_GF\_p] Cryptographic operation

| Hierarchical to:    | No other components.                                                                                                                                                                                                                                                        |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCS_COP.1.1[ECC_GF_ | [p] The TSF shall perform <i>signature generation and verification</i><br>in accordance with the specified cryptographic algorithm <i>ECC</i><br><i>over GF(p)</i> and cryptographic key sizes <i>192 to 544 bits</i> that<br>meet the following: <i>ISO 14888-3 [29]</i> . |

| Application Notes:  | The TOE also supports key lengths of 128 to 191 bits. For AVA_VAN.5 these are not considered sufficient. Therefore only keys of least 192 bits are listed here.                                                                                                             |

PUBLIC

| Dependencies:       | [FDP_ITC.1 Import of user data without security attributes, or<br>FDP_ITC.2 Import of user data with security attributes, or<br>FCS_CKM.1 Cryptographic key generation]<br>FCS_CKM.4 Cryptographic key destruction.                                                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FCS_COP.1[ECC_ADD]  | Cryptographic operation                                                                                                                                                                                                                                                    |

| Hierarchical to:    | No other components.                                                                                                                                                                                                                                                       |

| FCS_COP.1.1[ECC_ADD | P]The TSF shall perform secure point addition in accordance<br>with the specified cryptographic algorithm ECC over GF(p)<br>and cryptographic key sizes 192 to 544 bits that meet the<br>following: ISO 14888-3 [29].                                                      |

| Application Notes:  | The point addition does not have a key. The key size given is related to the length of the supported operand lengths.                                                                                                                                                      |

|                     | The TOE also supports length from 128 to 191 bits. For AVA_VAN.5 these are not considered sufficient. Therefore only lengths of at least 192 bits are listed here.                                                                                                         |

| Dependencies:       | [FDP_ITC.1 Import of user data without security attributes, or<br>FDP_ITC.2 Import of user data with security attributes, or<br>FCS_CKM.1 Cryptographic key generation]<br>FCS_CKM.4 Cryptographic key destruction.                                                        |

| FCS_COP.1[ECC_DHKE  | ]Cryptographic operation                                                                                                                                                                                                                                                   |

| Hierarchical to:    | No other components.                                                                                                                                                                                                                                                       |

| FCS_COP.1.1[ECC_DHK | [E] The TSF shall perform <i>Diffie-Hellman Key Exchange</i> in accordance with the specified cryptographic algorithm <i>ECC over GF(p)</i> and cryptographic key sizes <i>192 to 544 bits</i> that meet the following: <i>ISO 11770-3 [30]</i> .                          |

| Application Notes:  | (1) The TOE also supports key lengths of 128 to 191 bits. For<br>AVA_VAN.5 these are not considered sufficient. Therefore<br>only keys of least 192 bits are listed here.                                                                                                  |